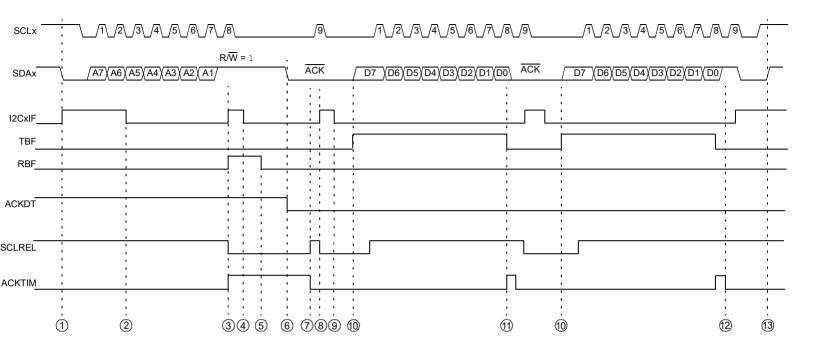

- ① Detecting Start bit enables address detection, interrupt is set if the SCIE bit is set.

- User software clears the interrupt flag.

- 3 Client receives the address byte with RW = 1. Hardware clears SCLREL to suspend host clock. ACKTIM and interrupt flag are asserted.

- 4 User software clears the interrupt flag.

- (5) Software reads the I2CxRV register, that clears the RBF flag.

- $\bigcirc$  ACKDT is written with  $\overline{\text{ACK}}$ .

- ① User software sets SCLREL to release clock hold. Host clocks in the Acknowledgment sequence. ACKTIM is cleared by hardware.

- (8) Hardware clears SCLREL to suspend host clock if  $R/\overline{W} = 1$ .

- 9 User software clears the interrupt flag.

- (i) User software loads the I2CxTRN register with response data. TBF = 1 indicates that the buffer is full.

- 1 After last bit, module clears TBF bit, indicating buffer is available for next byte.

- (2) At the end of ninth clock, if host sent NACK, no more data is expected. Module does not suspend the clock.

- 13 Module recognizes Stop event.