## **Timer Setup:**

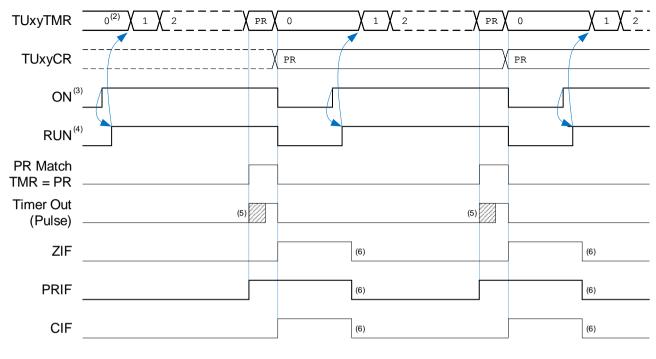

START = None (ON = 1) CSYNC = Sync RESET = At PR Match OSEN = Enabled STOP = At PR Match

## Note:

- 1. Cross-domain clock synchronization applies as required but is not highlighted.

- 2. Ensure that TUxyTMR counter is reset to zero by setting CLR command.

- 3. The ON bit is set in the software and cleared by hardware upon Stop (one-shot mode).

- 4. The RUN trace illustrates the internal Timer Clock domain run/stop signal. Clock sync delays apply before the value appears in the RUN SFR bit.

- 5. The uncertainty of the output is due to the prescaler setting.

- 6. Cleared by software.