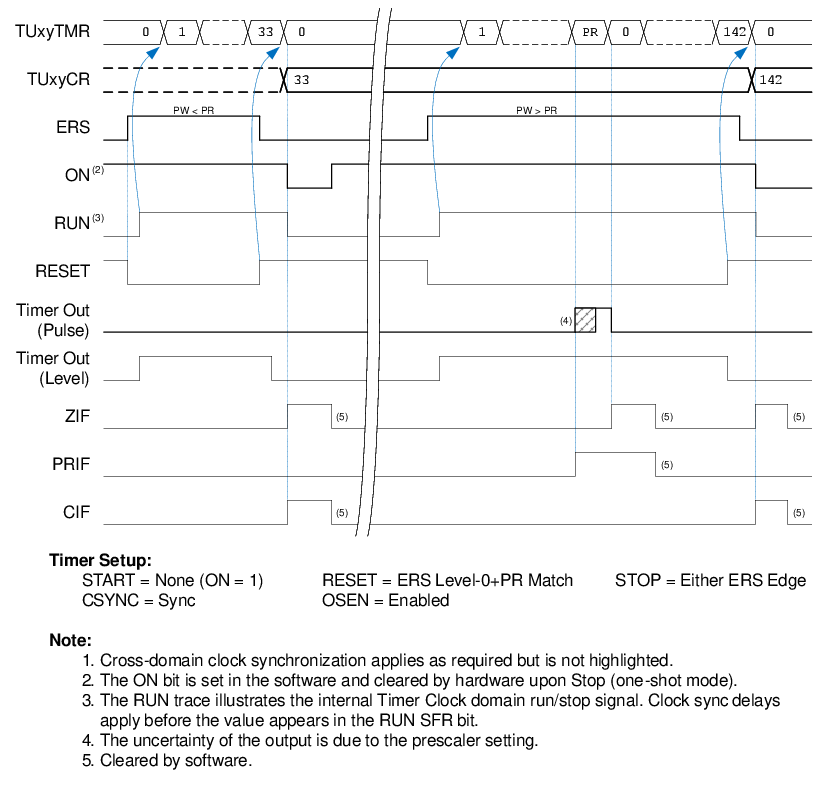

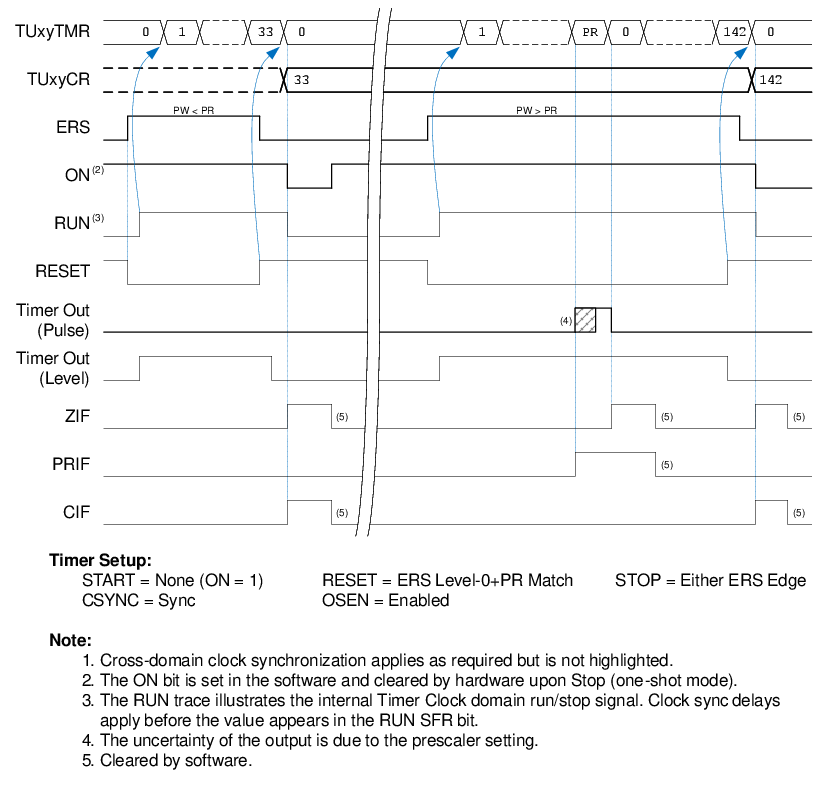

The timer can be configured to test if the ERS input has been high/low for a certain period of time as per the settings shown in Table 2-7.

| Timer Setting | Value |

|---|---|

| START | None (ON = 1) |

| RESET | ERS Level-0 + PR Match |

| STOP | Either ERS Edge |

| CSYNC (Clock Sync) | Sync |

| EPOL (ERS Polarity) |

True Level (to test for stuck-high) Inverted Level (to test for stuck-low) |

| OSEN (One-shot) |

Enabled (for one-shot) Disabled (for auto-repeat) |

| PR (Period Register) | Desired time period to test |

When the input rises (from 0 to 1), the counter will begin to count. When a

PR match occurs, PRIF will occur indicating that the input has been stuck at high for a

desired long enough time period. The counter resets and continues counting, and ZIF is

set. When ERS falls, the timer stops counting, CIF is set, and TUxyCR captures the

length of the pulse. The OSEN bit can be set to make it a one-shot operation, and

cleared for auto-repeat operation. This is shown in Figure 2-9. If testing for stuck-low, set EPOL =

1.Figure 1. Input Stuck High