|

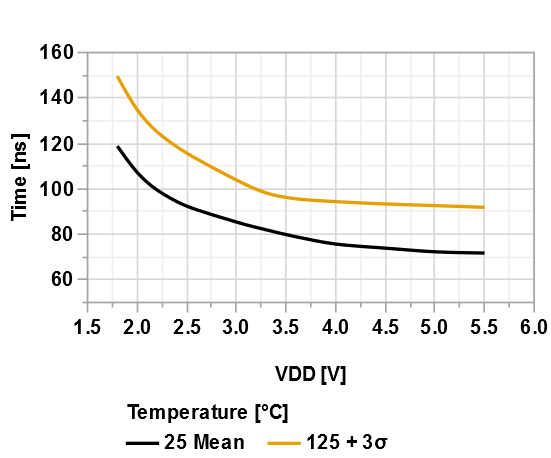

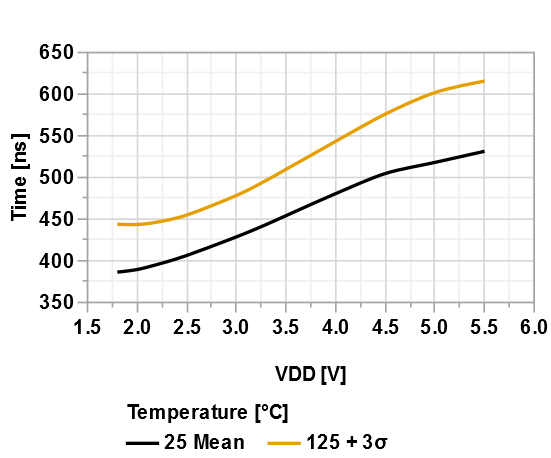

Figure 1. Falling Edge

Response Time vs. VDD (VCM =

VDD/2, CTRLA.POWER =

0x00)

|

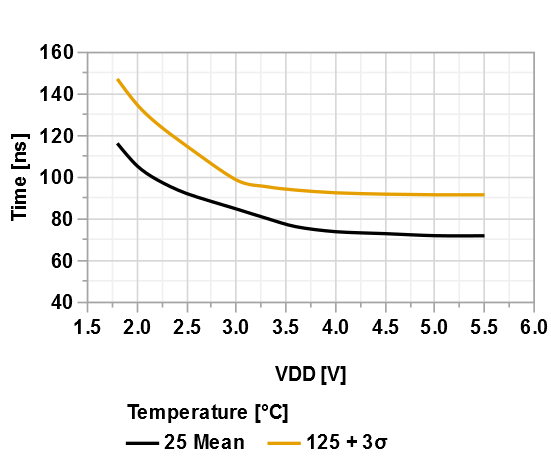

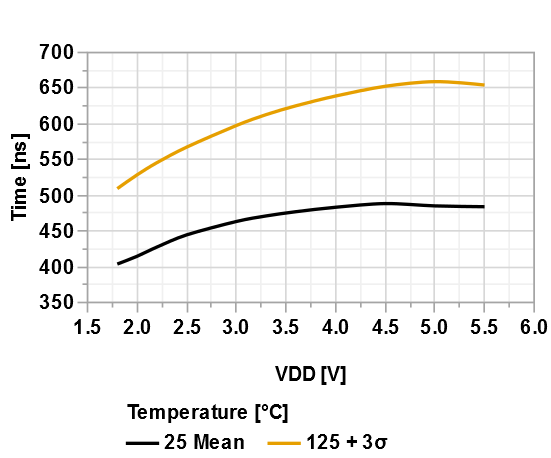

Figure 2. Rising Edge

Response Time vs. VDD (VCM =

VDD/2, CTRLA.POWER =

0x00)

|

|

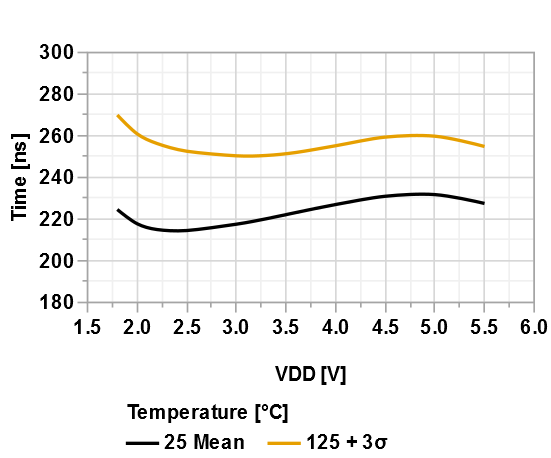

Figure 3. Falling Edge

Response Time vs. VDD (VCM =

VDD/2, CTRLA.POWER =

0x01)

|

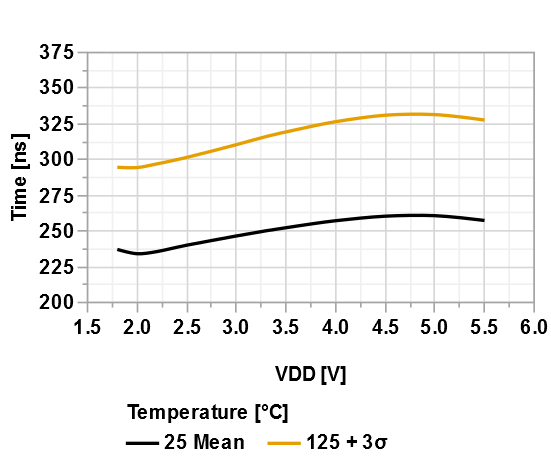

Figure 4. Rising Edge

Response Time vs. VDD (VCM =

VDD/2, CTRLA.POWER =

0x01)

|

|

Figure 5. Falling Edge

Response Time vs. VDD (VCM =

VDD/2, CTRLA.POWER =

0x02)

|

Figure 6. Rising Edge

Response Time vs. VDD (VCM =

VDD/2, CTRLA.POWER =

0x02)

|

|

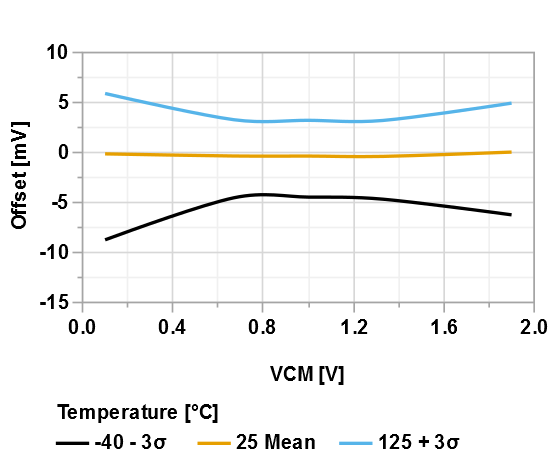

Figure 7. Input Offset

vs. Common Mode Voltage (VDD = 2.0V)

|

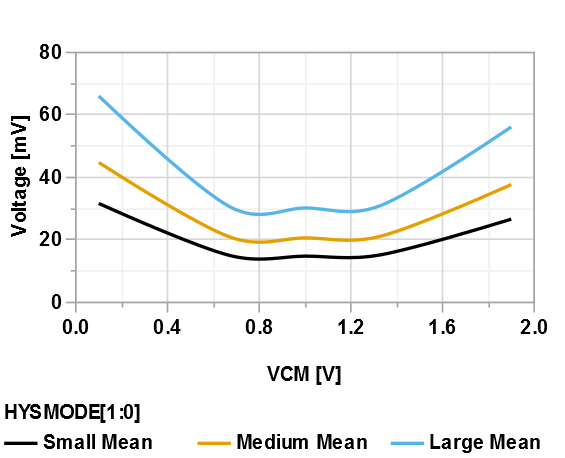

Figure 8. Input

Hysteresis vs. Common Mode Voltage (VDD =

2.0V)

|

|

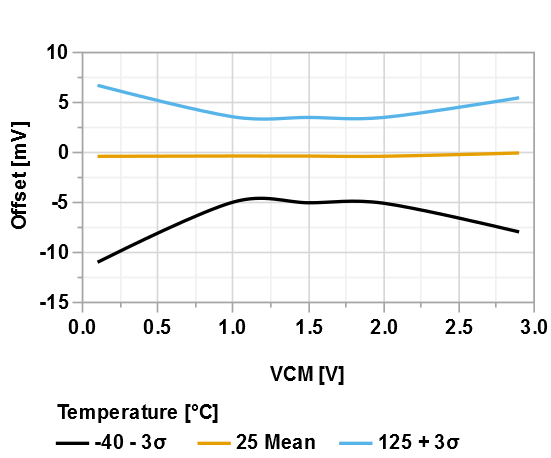

Figure 9. Input Offset

vs. Common Mode Voltage (VDD = 3.0V)

|

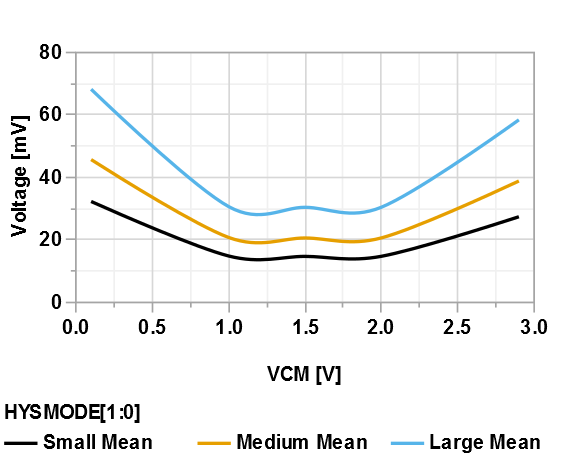

Figure 10. Input

Hysteresis vs. Common Mode Voltage (VDD =

3.0V)

|

|

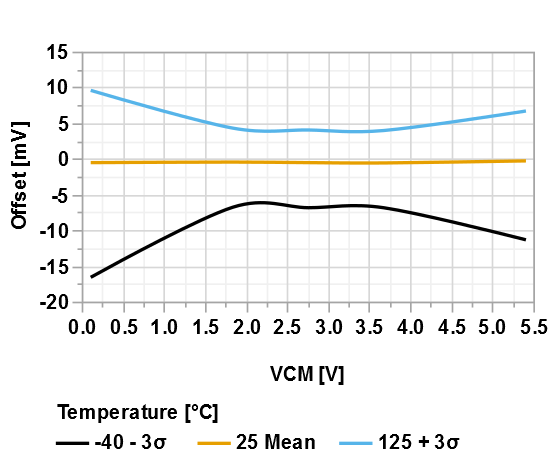

Figure 11. Input Offset

vs. Common Mode Voltage (VDD = 5.5V)

|

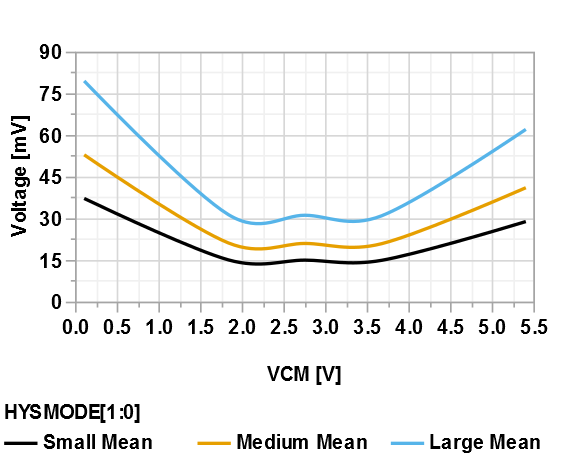

Figure 12. Input

Hysteresis vs. Common Mode Voltage (VDD =

5.5V)

|