Split Mode Overview

To double the number of timers and PWM channels in the TCA, a Split mode is provided. In this Split mode, the 16-bit timer/counter acts as two separate 8-bit timers, which each have three compare channels for PWM generation. The Split mode will only work with single-slope down-count. Event controlled operation is not supported in Split mode.

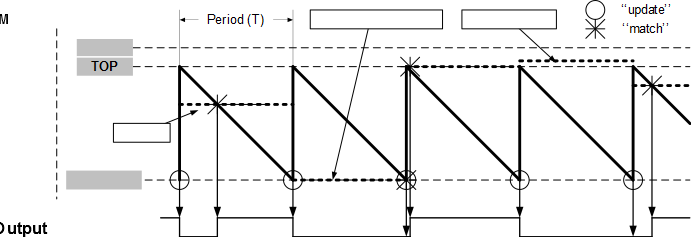

The figure below shows single-slope PWM generation in Split mode. The waveform generator output is cleared at BOTTOM, and set on compare match between the counter value (TCAn.CNT) and the Compare n (TCAn.CMPn) register.

Activating Split mode results in changes to the functionality of some registers and register bits. The modifications are described in a separate register map (see Register Summary - Split Mode).

Split Mode Differences Compared to Normal Mode

- Count:

- Down-count only

- Low Byte Timer Counter (TCAn.LCNT) register and High Byte Timer Counter (TCAn.HCNT) register are independent

- Waveform generation:

- Single-slope PWM only (WGMODE = SINGLESLOPE in the TCAn.CTRLB register)

- Interrupt:

- No change for Low Byte Timer Counter (TCAn.LCNT) register

- Underflow interrupt for High Byte Timer Counter (TCAn.HCNT) register

- No compare interrupt or flag for High Byte Compare n (TCAn.HCMPn) register

- Event Actions: Not compatible

- Buffer registers and buffer valid flags: Unused

- Register Access: Byte access to all registers

Block Diagram

Split Mode Initialization

When shifting between Normal mode and Split mode, the functionality of some registers

and bits changes, but their values do not. For this reason, disabling the peripheral

(ENABLE = 0 in the TCAn.CTRLA register) and doing a hard Reset (CMD

= RESET in the TCAn.CTRLESET register) is recommended when changing the mode to

avoid unexpected behavior.

- 1.Enable Split mode by writing

a ‘

1’ to the Split mode enable (SPLITM) bit in the Control D (TCAn.CTRLD) register. - 2.Write a TOP value to the Period (TCAn.PER) registers.

- 3.Enable the peripheral by

writing a ‘

1’ to the Enable (ENABLE) bit in the Control A (TCAn.CTRLA) register.The counter will start counting clock ticks according to the prescaler setting in the Clock Select (CLKSEL) bit field in the TCAn.CTRLA register.

- 4.The counter values can be read from the Counter bit field in the Counter (TCAn.CNT) registers.