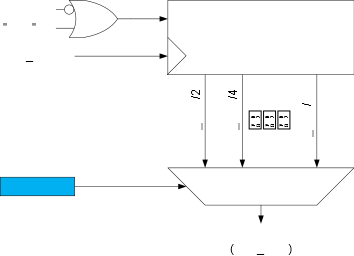

The ADC peripheral contains a prescaler which generates the ADC clock (CLK_ADC) from the peripheral clock (CLK_PER). The minimum ADC_CLK frequency is 150 kHz. The prescaling is selected by writing to the Prescaler (PRESC) bit field in the Control C (ADCn.CTRLC) register. The prescaler begins counting from the moment the ADC conversion starts and is reset for every new conversion. Refer to Figure 1.

When initiating a conversion by writing a

‘1’ to the Start Conversion (STCONV) bit in the ADCn.COMMAND register

or from event, the conversion starts after one CLK_PER cycle. The prescaler is kept in

Reset, as long as there is no ongoing conversion. This assures a fixed delay from the

trigger to the actual start of a conversion of maximum 2 CLK_PER cycles.