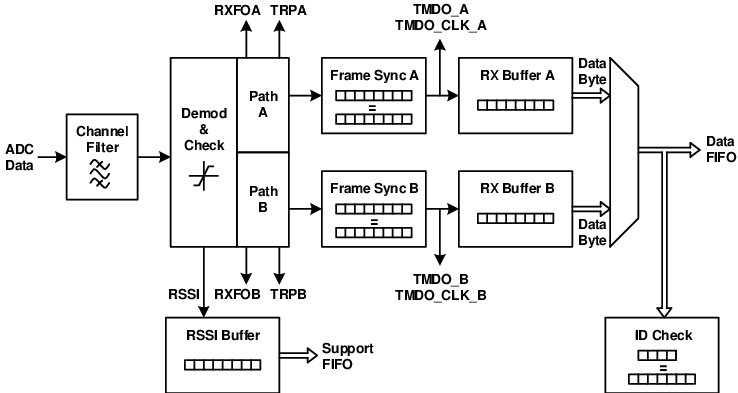

The RX Digital Signal Processing (DSP) block performs the digital filtering, decoding, checking and byte-wise buffering of the RX samples that are derived from the ADC illustrated in the following figure. The RX DSP provides the following outputs:

- Raw demodulated data at the TRPA/B pins

- Decoded data at the TMDO and TMDO_CLK pins

- Buffered data bytes toward the data FIFO and ID check block

- Auxiliary information about the

signal, such as the RSSI and the frequency offset of the received signal from the

selected center frequency (RXFOA/B)Figure 1. RX DSP Overview

The channel filter determines the receiver bandwidth. Its output is used for both receiving paths A and B, making it necessary to configure the filter to match both paths. The receiving paths A and B are identical and consist of an ASK and FSK demodulator with attached signal checks, a frame synchronizer that supports pattern-based searches for the telegram start and a 1-byte hardware buffer with integrated CRC checker for the received data.

Depending on the signal checks, one path is selected to write the received data to the data FIFO and optionally to the ID check block.

The RSSI values are determined by the demodulator and written via the RSSI buffer to the support FIFO where the latest 16 values are stored for further processing.