When the system controller SPI is configured as a master, a device can program itself. In SPI master programming, the programming images are stored in the external SPI flash memory using the SPI directory. For more information about the SPI directory and about programming the external SPI flash memory, see Programming the External SPI Flash.

SPI master programming supports auto update and IAP. In auto update programming, if the version of the update image is found to be different from the currently programmed version, the system controller reads the update image bitstream from the external SPI flash memory and programs the device on power-up. In IAP, the user application initiates the device program, and the system controller reads the bitstream from the external SPI flash memory to program the device. The auto update and IAP operations are atomic and cannot be interrupted by JTAG or SPI slave commands.

The Auto Update feature is not enabled by default and if required, this needs to be enabled using Libero SoC. SPI Master mode also supports Auto Programming and Auto Recovery, see Table 1. These two features are enabled by default and do not require user configuration.

For information about the I/O states during SPI master programming, see I/O States During Programming.

The following table lists the initiation sources for the features supported by SPI master programming.

| Programming Feature | Description | Initiation Source |

|---|---|---|

| Auto programming | Programs a blank device | Device reset or power-cycle |

| Auto update | Updates device contents automatically | Device reset, power-cycle, or system service request |

| IAP | Updates device contents upon user request | System service request |

| Auto recovery1 | Automatically recovers the device from programming failure | Device power failure during programming |

| 1 If there is a power interruption while Auto update or IAP is updating the sNVM, then the auto-recovery is not triggered. Though, if the sNVM is not updated completely because of a power interruption, the device starts up and will attempt to boot as normal. However, the partially programmed sNVM causes the user design to malfunction. In this case, the user needs to use the VERIFY action or Digest Check to determine if the programming is successful. | ||

For information about implementing Auto update and IAP, see AC466: PolarFire FPGA Auto Update and In-Application Programming Application Note.

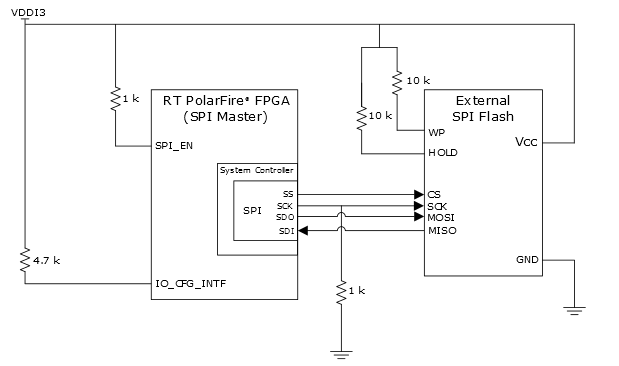

The following figure shows the recommended board configuration for SPI master programming. The VDDI3 must match the voltage specified in the datasheet associated with the external SPI flash.