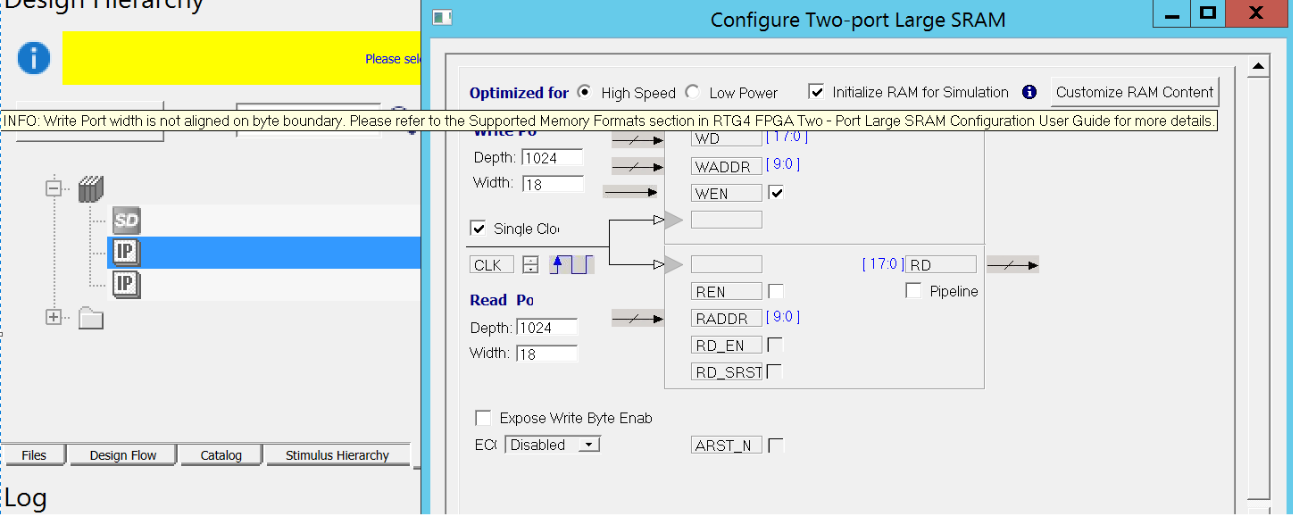

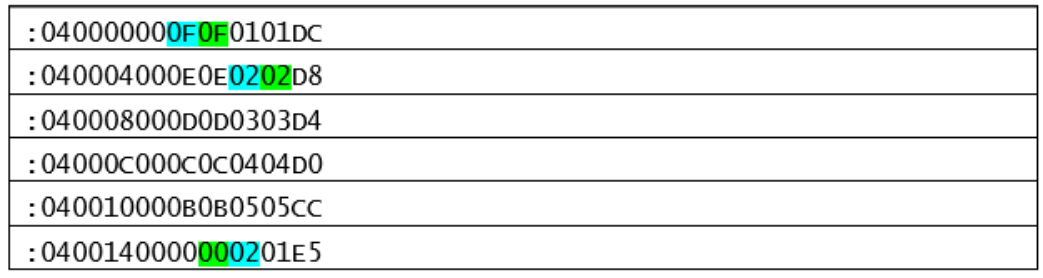

Consider the following Intel HEX memory file.

Figure 1. Memory File Data - Intel HEX

Memory File

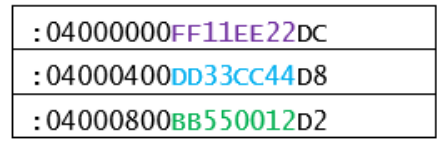

The binary stream of bits for above memory file data is:

If the memory port width is 4 bits, the tool reads 8 bits at a time from the binary

stream above. For the 8 bits, you must pad zeros for the upper 4 bits and specify the

actual data in the lower 4 bits, as shown in the following figure.

Figure 2. Padding Zeros for the Upper 4 Bits and Specifying Data in the Lower 4

Bits

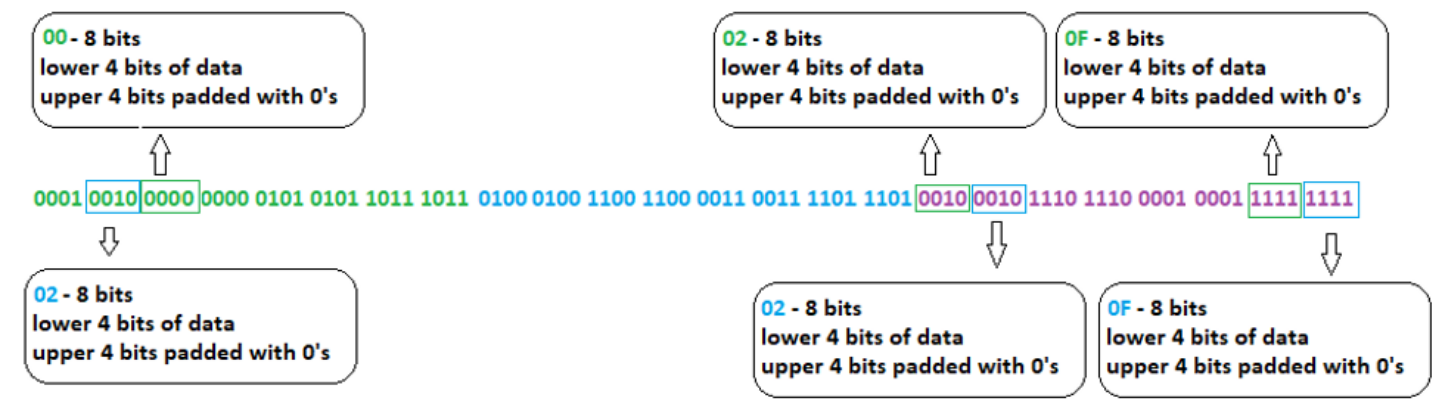

The following figure shows the equivalent memory file data padded with zeros to achieve a 4-bit write port width.

Figure 3. Equivalent Memory File Data Padded with Zeros (4-bit Write Port Width)

When the tool parses the above memory file data (padded with zeros), it converts the data to binary and reads it as a stream of bits. If the port width is 4 bits, the tool reads 8 bits (byte-aligned), ignores the upper 4 bits of actual data, and stores the lower 4 bits of actual data in RAM, as shown in the following table.

| Address | Data |

|---|---|

| 0 | 0xF |

| 1 | 0xF |

| 2 | 0x1 |

| 3 | 0x1 |

| 4 | 0xE |

| 5 | 0xE |

| 6 | 0x2 |

| 7 | 0x2 |

| 8 | 0xD |

| 9 | 0xD |

| A | 0x3 |

| B | 0x3 |

| C | 0xC |

| D | 0xC |

| E | 0x4 |

| F | 0x4 |

| 10 | 0xB |

| 11 | 0xB |

| 12 | 0x5 |

| 13 | 0x5 |

| 14 | 0x0 |

| 15 | 0x0 |

| 16 | 0x2 |

| 17 | 0x1 |

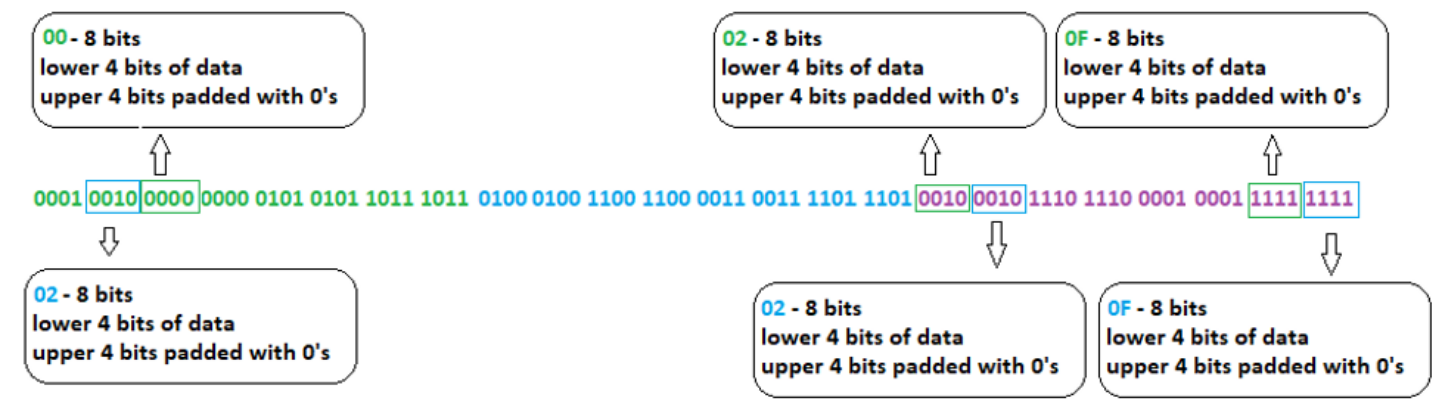

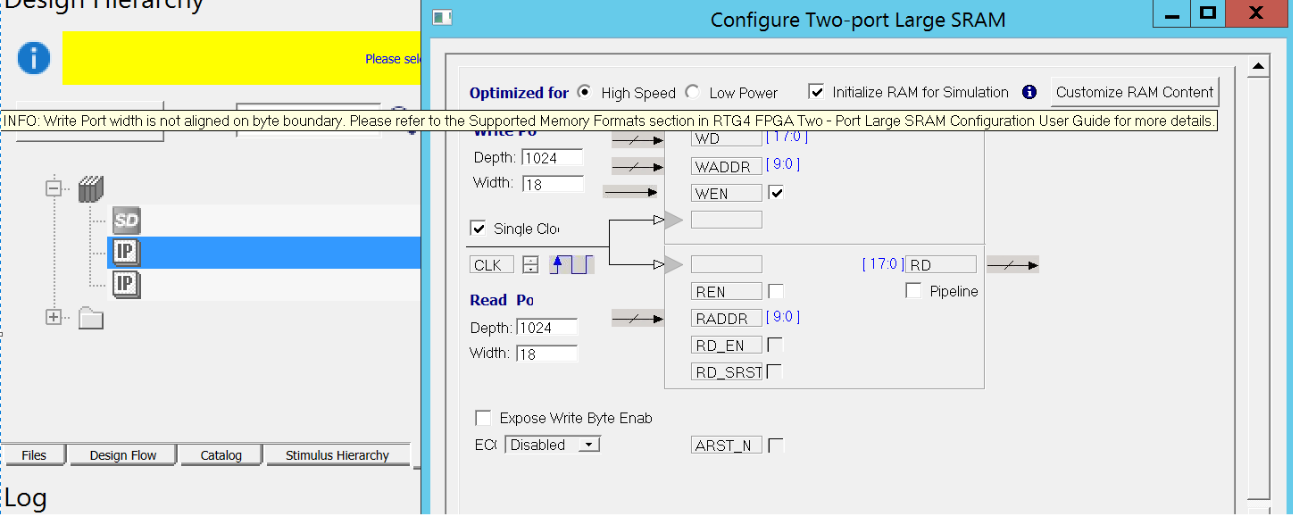

Note: x1 and x2 port widths are handled

using the same technique of padding zeros. You always zero pad to the next

8-bit-width increment (8, 16, 24, and so on). If a write port width is not aligned

on a byte boundary, the following message appears.

Figure 4. Message when a Write Port

Width is Not Aligned on a Byte Boundary