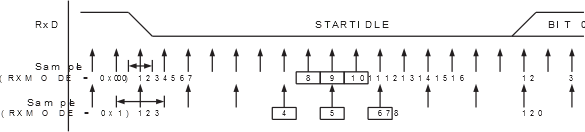

The clock recovery unit synchronizes the

internal clock to the incoming serial frames. Figure 1 illustrates the sampling process for the Start bit of an

incoming frame:

- In Normal mode, the sample rate is 16 times the baud rate.

- In Double-Speed mode, the sample rate is eight times the baud rate.

- The horizontal arrows illustrate the synchronization variation due to the sampling process. Note that in Double-Speed mode, the variation is larger.

- Samples denoted as zero are sampled with the RxD line idle (i.e., when there is no communication activity).

Figure 1. Start Bit Sampling

When the clock recovery logic detects a

high-to-low (i.e., idle-to-start) transition on the RxD line, the Start bit detection

sequence is initiated. Sample 1 denotes the first zero-sample, as shown in the figure. The

clock recovery logic then uses three subsequent samples (samples 8, 9, and 10 in Normal

mode, samples 4, 5, and 6 in Double-Speed mode) to decide if a valid Start bit is received:

- If two or three samples have a low level, the Start bit is accepted. The clock recovery unit is synchronized, and the data recovery can begin.

- If two or three samples have a high level, the Start bit is rejected as a noise spike, and the receiver looks for the next high-to-low transition.