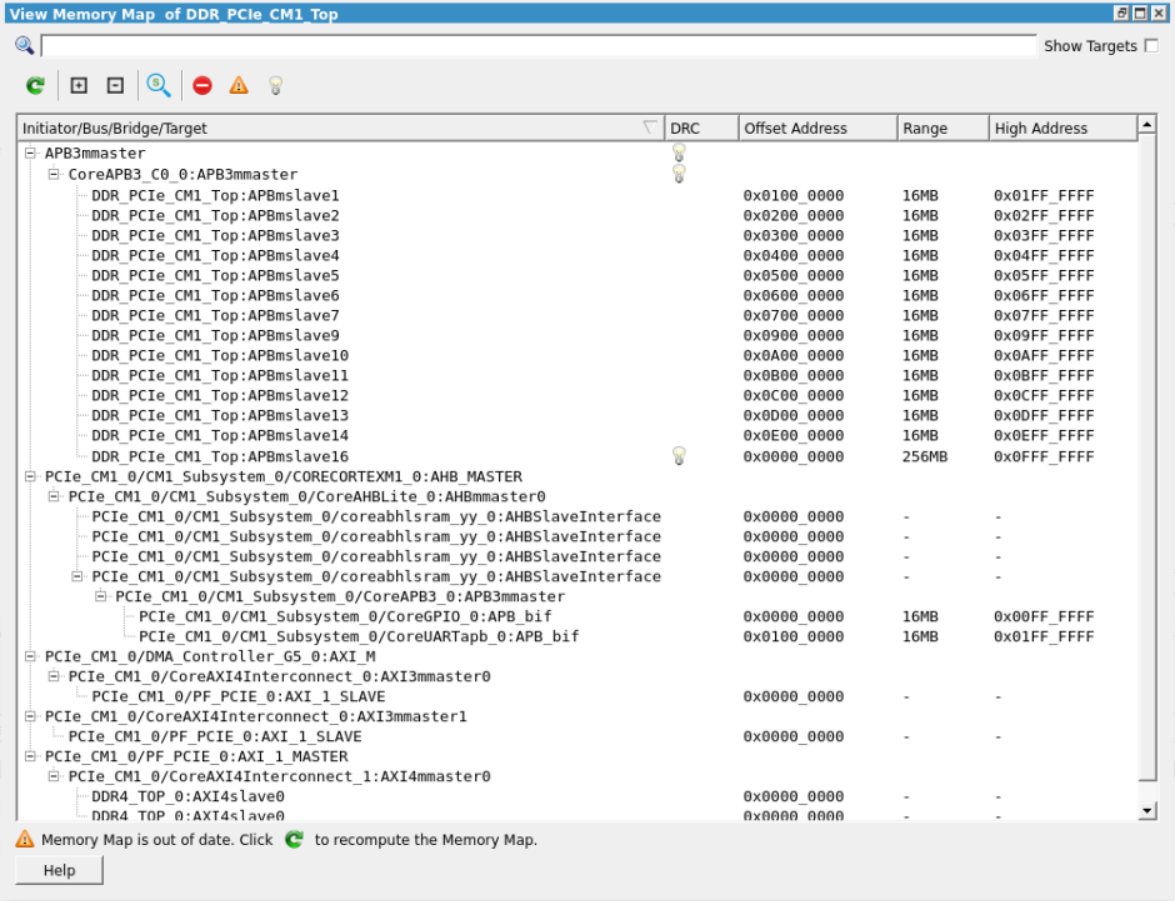

The View Memory Map window constructs the memory map corresponding to various initiators in the

SmartDesign component and displays the hierarchy in a tree format. To open the window,

right-click anywhere on the SmartDesign canvas and select View Memory

Map. Click the View Memory Map icon ![]() in the toolbar at the top of the canvas.

in the toolbar at the top of the canvas.

This window shows the memory map starting from an initiator in the design to targets connected through bus and bridge cores hierarchically. There can be various types of bus and bridge cores in the hierarchy between the initiator and the targets.

Initiator Node > Bus > Bridge > Bus > Targets

Initiator Node > Bus > Targets

Each target in the memory map is shown with an Offset Address, Range, High Address, and Design Rule Check (DRC). If DRC exists, an Error or a Warning icon with a tool-tip message is shown. DRC is flagged if a target cannot be accessed completely or partially by the initiator’s address space.

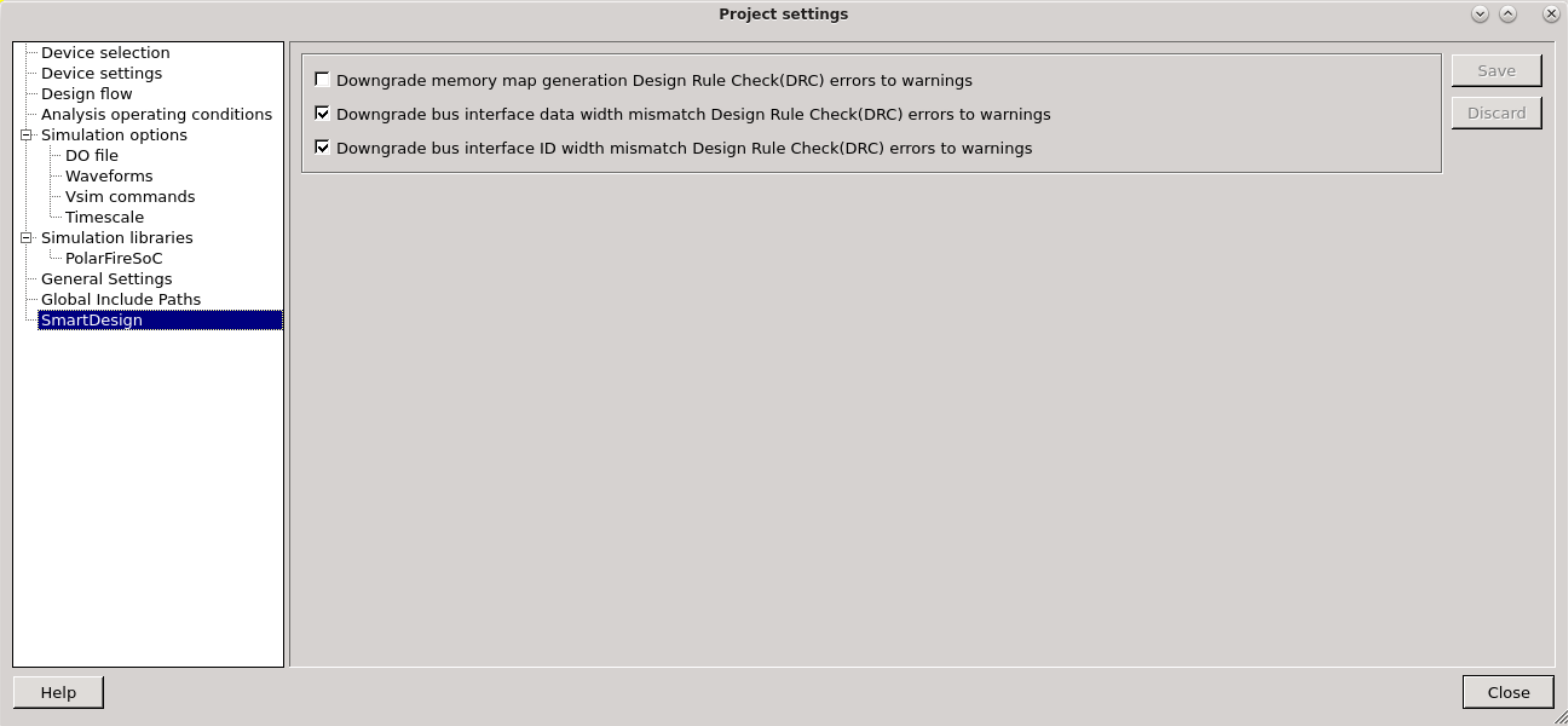

If there are any DRCs in the Memory Map corresponding to a Smart Design component and its hierarchy, they are flagged when the SmartDesign component is generated and is printed as messages to the Libero log window. If the DRC are warnings, the SmartDesign component generation passes; however, if the DRCs are errors, the SmartDesign component generation fails. There is an option to downgrade Memory Map DRC errors to warnings and let the SmartDesign component generation to go through without failing.

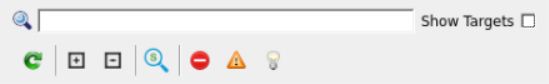

Navigation Actions and Filters

The View Memory Map window also provides new buttons and filters at the top of the window for easy navigation and ease of use.

Search

You can search for a specific initiator, bus, bridge, and target in the memory map by specifying a full or partial name in the search box.

-

Show Targets

Shows all the initiators and targets under them in the design in a flat hierarchy with their start addresses, ranges and DRCs if any. The initiators, bus, and bridge cores are not shown.

-

Refresh

Updates the content of the Memory map. It becomes active only when something is changed on canvas.

-

Expand

Expands and shows the full hierarchy of all initiators in the memory map starting from the initiator to the targets.

-

Collapse

Collapses the full hierarchy of all initiators in the memory map and only shows the top-level initiators in the window.

-

Zoom and Center

Toggle action. If checked, the canvas zooms to the selected item after every selection.

- DRC Filters

It filters the DRC messages, if any. It categorized the message on the basis of severity: error, warning, and information.

Additional Memory Map functions allow you to sort items by their Offset or High addresses and ranges.

Click the columns of the header to sort the items in ascending or descending order.

Click the first column of the header to see the initial view of the table.

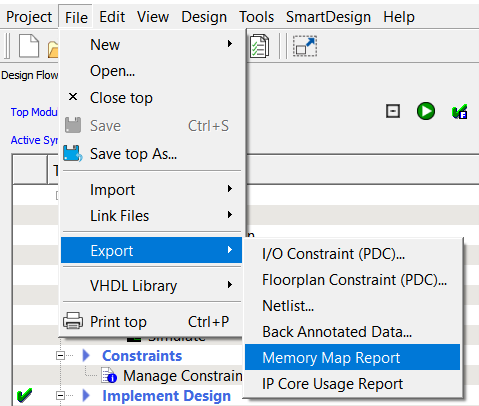

Exporting Memory Map Report

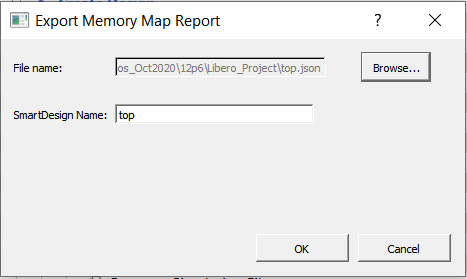

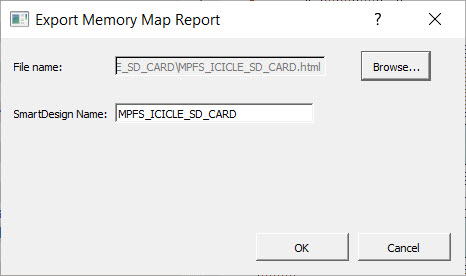

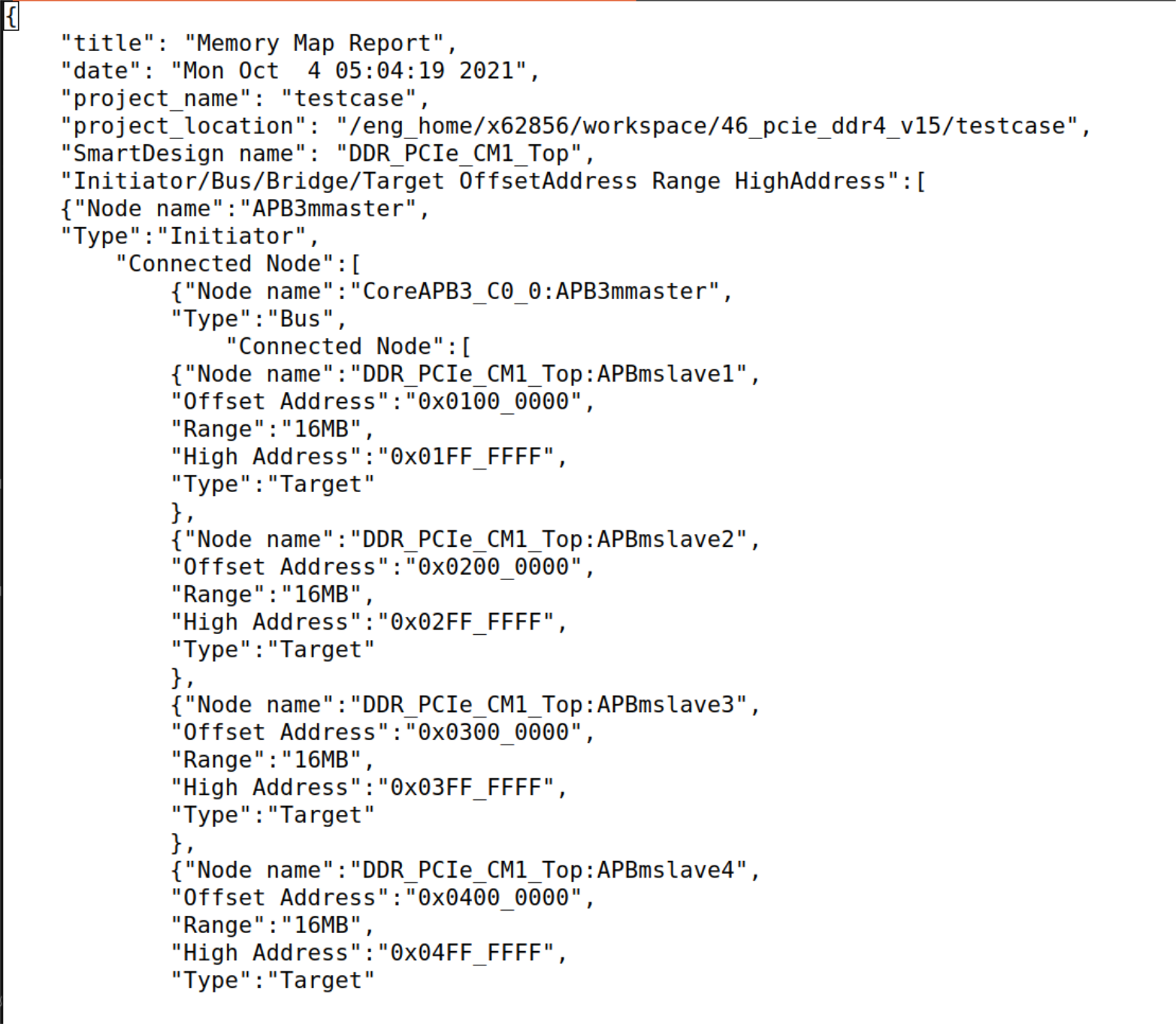

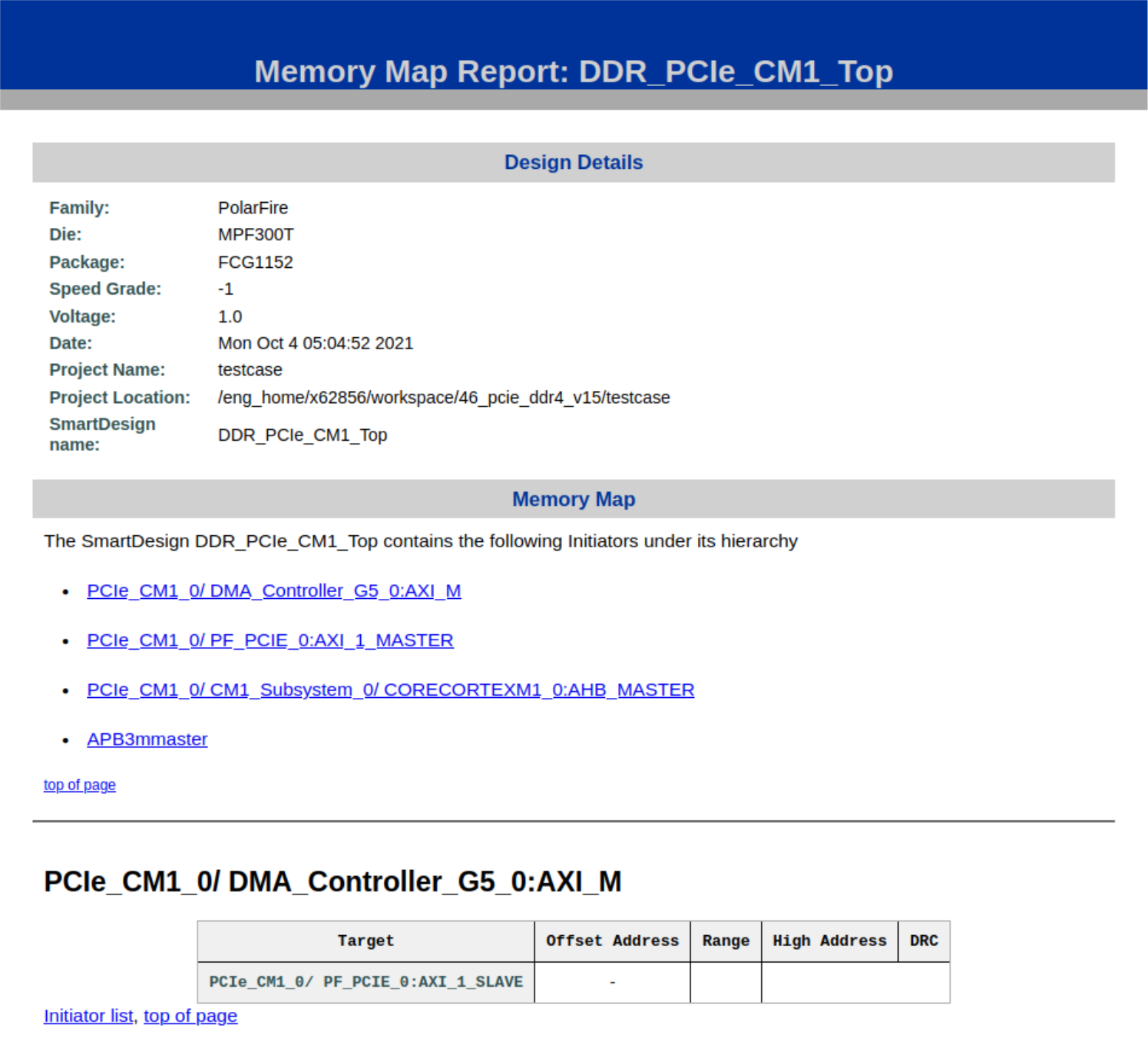

The memory map can also be exported to a JSON or HTML file. Select the Memory Map

Report option from Libero File > Export. In the

Export Memory Map Report window, you can specify the SmartDesign

component for which you want to export the memory map report. Click on the Browse

button in the window to specify the memory map report file name, type

(.json or .html) and location on disk. A

.json or .html format memory map report file (which can be

opened in a web browser or a json viewer in a text editor) is created when you click the

Save button.

Initiators, Bus, and Bridge cores available in Libero SoC Catalog

Various types of cores recognized as initiators, bus, and bridge cores are available in the Libero SoC Catalog window that can be used in a design. There are a few limitations on some of the core versions that can be used in a design for the memory map to be constructed correctly. The following consolidated table of all the available initiators, and bus and bridge cores highlights those limitations and exceptions on the cores and core versions with respect to memory map.

| Classification | Core | Core Type | Minimum core version supported in Libero® SoC v2021.2 for Memory Map generation | Latest core version available in Libero SoC v2021.2 |

| Initiators | MIV_RV32IMC | AXI, AHBLite and APB3 Initiators | NA. All available production version works. | 2.1.100 |

| MIV_RV32 | AXI, AHBLite and APB3 Initiators |

NA. All available production version works. | 3.0.100 | |

| MIV_RV32IMA_L1_AXI | AXI Initiator | NA. All available production version works. | 2.1.100 | |

| MIV_RV32IMA_L1_AHB | AHBLite Initiator | NA. All available production version works. | 2.3.100 | |

| MIV_RV32IMAF_L1_AHB | AHBLite Initiator | NA. All available production version works. | 2.1.100 | |

| CORERISCV_AXI4 | AXI4 Initiator | NA. All available production version works. | 2.0.102 | |

| COREAXI4DMACONTROLLER | AXI4 Initiator | NA. All available production versions works. | 2.0.100 | |

| COREABC | APB3 Initiator | NA. All available production versions works. | 3.8.102 | |

| Family specific Initiator cores | PolarFire® SoC Standalone MSS (PolarFire SoC only) | AXI4 Initiator | NA. All available production version works. | v2.0 |

| System Builder and SmartFusion®2 MSS (SmartFusion2 and IGLOO®2) | AHBLite and APB3 Initiators | NA. All available production version works. | 1.1.500 | |

| CORECORTEXM1(PolarFire, PolarFire SoC and RTG4™) | AHBLite Initiator | NA. All available production version works. | 3.0.100 and 2.0.100 | |

| PF_PCIE (PolarFire only) | AXI Initiator | NA. All available production version works. | 2.0.104 | |

| SERDES_IF, SERDES_IF2, SERDES_IF3 (SmartFusion2 and IGLOO2) | AXI and AHBLite Initiators | NA. All available production version works. | 1.2.210, 1.2.212, 1.2.212 respectively | |

| PCIE_SERDES_IF (RTG4 only) | AXI and AHBLite Initiators | NA. All available production version works. | 2.0.100 |

|

| COREHPDMACTRL (SmartFusion2 and IGLOO2) | AHBLite Initiator | NA. All available production version works. | 2.1.103 | |

| CORESYSSERVICES (SmartFusion2 and IGLOO2) | AHBLite Initiator | NA. All available production version works. | 3.2.102 | |

| CoreConfigMaster (SmartFusion2 and IGLOO2) | AHBLite Initiator | NA. All available production version works. | 2.1.102 | |

| Bus cores | COREAXI4INTERCONNECT | AXI bus | 2.5.100 | 2.8.103 |

| CoreAHBLite | AHBLite bus | NA. All available production version works. | 5.4.102 | |

| CoreAPB3 | APB3 bus | NA. All available production version works. | 4.1.100 | |

| CoreAXI | AXI bus | NA. All available production version works. | 3.2.101 | |

| Family specific bus type cores | PF_DRI (PolarFire and PolarFire SoC) | APB bus | This core is not supported for Memory Map generation. Correct addresses and/or hierarchy is not shown for this core in the Memory Map of Libero SoC v2021.2. | 1.1.100 |

| CoreConfigP (SmartFusion2 and IGLOO2) | APB bus | NA. All available production version works. | 7.1.100 | |

| Bridge cores | COREAXITOAHBL | AXI to AHBLite bridge | Must use v3.5.100 for proper Memory Map generation in Libero SoC v2021.2. | 3.5.100 |

| COREAHBL2AHBL_BRIDGE | AHBLite to AHBLite bridge | This core is not supported for Memory Map generation. Correct addresses and/or hierarchy is not shown for this core in the Memory Map of Libero SoC v2021.2. Supported in a future release. | 2.1.108 | |

| COREAHBLTOAXI | AHBLite to AXI bridge | NA. All available production version works. | 2.1.101 | |

| COREAHBTOAPB3 | AHBLite to APB bridge | NA. All available production version works. | 3.1.100 | |

| COREAXITOAXICONNECT | AXI to AXI bridge | This core is not supported for Memory Map generation. Correct addresses and/or hierarchy is not shown for this core in the Memory Map of Libero SoC v2021.2. Supported in a future release. | 2.0.101 |