For all the following design objects, drag and drop or right click Object > Instantiate to instantiate the design objects:

- IP cores—There are two methods for instantiating IP cores:

- Drag the IP core from the IP catalog and drop in the SmartDesign canvas. This prompts to enter the name of a component; you can configure the IP and click on OK. The configured IP generates and a component creates, and further this component instantiates into the canvas.

- In the IP catalog, right click on the core and chose the Configure Core menu, this prompts to enter the name of a component and you can configure the IP and click on OK a component generates. The component is available in the Project Manager Design Hierarchy tab or Component tab for drag and drop instantiation in the canvas.

- HDL files—To instantiate HDL modules, drag the HDL module from the Design Hierarchy into the SmartDesign Canvas.

- HDL Cores—HDL cores are typically parametrized HDL modules with or without bus interface ports. An HDL core is created from an HDL module in the Design Hierarchy. It is used to generate a core has been generated out of it (right click HDL file > Create Core from HDL). Drag and drop the HDL core module into the SmartDesign canvas. Parametrized HDL cores are configurable inside the SmartDesign canvas. Open the configurator to set the values for the parameters. An bus interface may also be added to the HDL core, and it shows up in the SmartDesign with a bus interface pin that can be used to easily connect to the appropriate bus IP core inside SmartDesign Canvas.

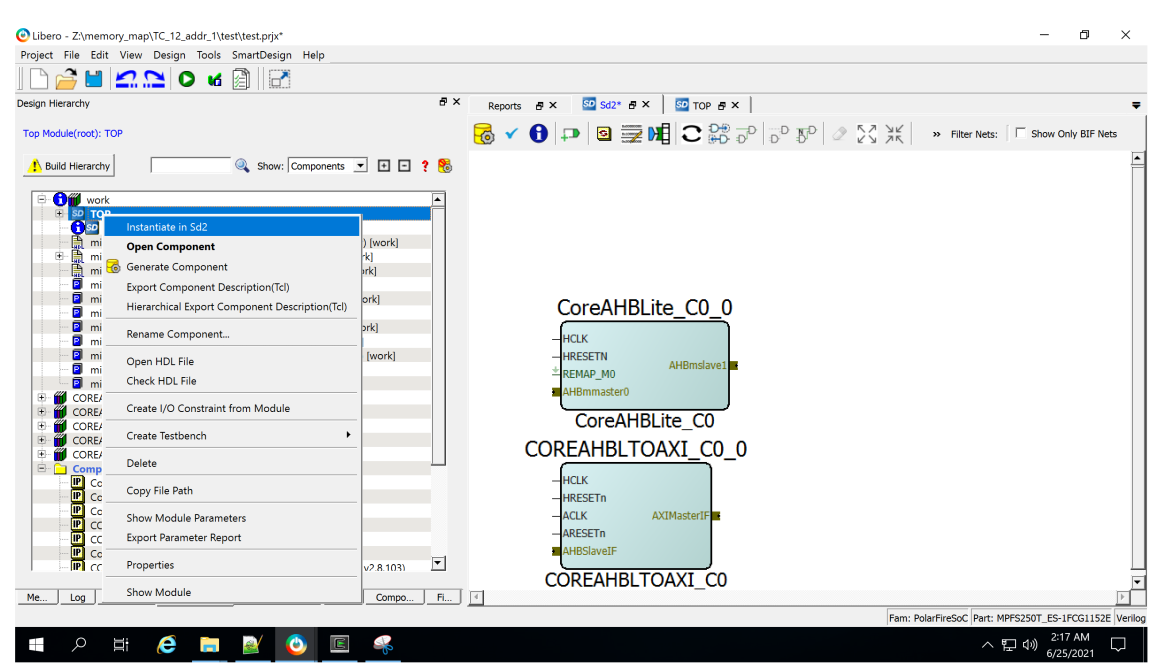

- Design Blocks file—Drag and drop the design blocks from the Design Hierarchy into the SmartDesign canvas. Design blocks are components whose layout might have been completed in a different Libero SoC project and exported/published for use in a top-level design as a component with placement and optional routing information. Design blocks are typically use to control timing for design blocks that have very tight timing constraints that are difficult to meet within the full design. The design blocks must be imported into the current Libero SoC project to be instantiated in SmartDesign. The following figure shows how to instantiate a design block.Figure 1. Design Block Instantiation

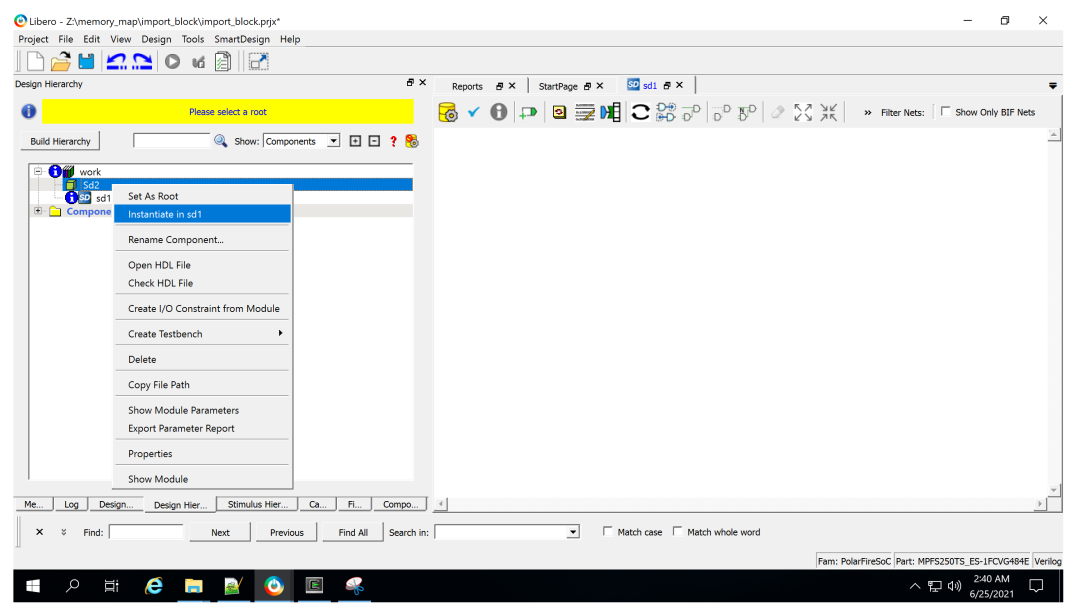

- SmartDesign Components—Another SmartDesign

component (

*.cxf) can be instantiated in the SmartDesign. Drag and drop the Smart Design component (*.cxf) from the Design Hierarchy into the SmartDesign canvas. Instantiation can also be performed by right clicking the module name in the Design Hierarchy and choosing Instantiate. The component (*.cxf) and its corresponding HDL files and IP cores must be imported into the current project and configured before instantiating in the new SmartDesign project.

Figure 2. SmartDesign Component Instantiation