One of the most common operations that needs to be performed when working with combinational logic is applying a delay (fixed number of clock cycles). The CCL can do this by writing the Filter Selection (FILTSEL) bit field in the LUT n Control A (CCL.LUTnCTRLA) registers.

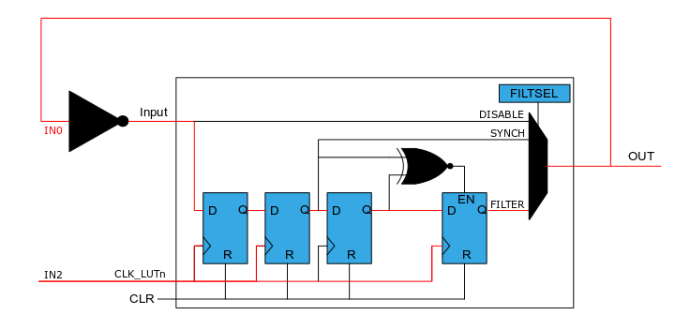

When FILTSEL=SYNCH, the configuration can be used to synchronize the output with CLK_LUTn and to obtain two CLK_LUTn cycles delays.

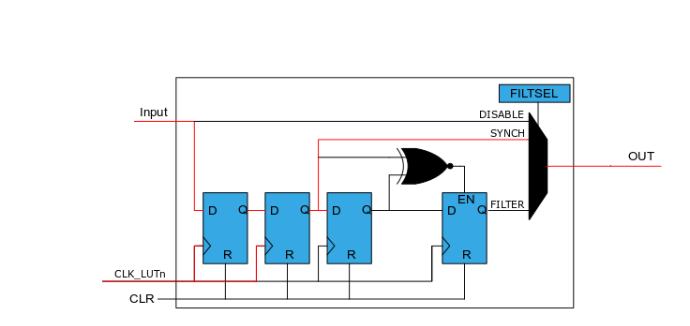

Using the LUT feedback feature, a divide by four configuration is obtained. The signal that will be divided must be used as clock input for the LUT and the output of the LUT must be linked to the input.

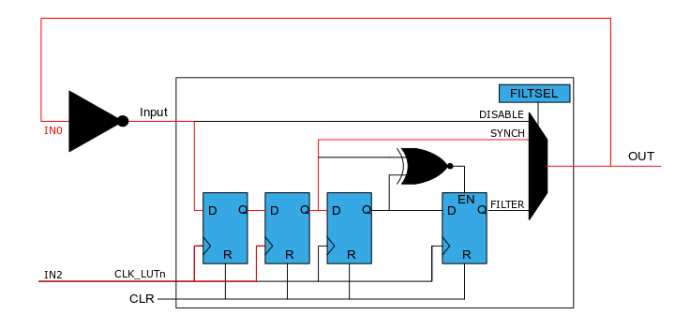

When FILTSEL=FILTER and input signal have at least four input clocks, the output will be delayed by four clock cycles.

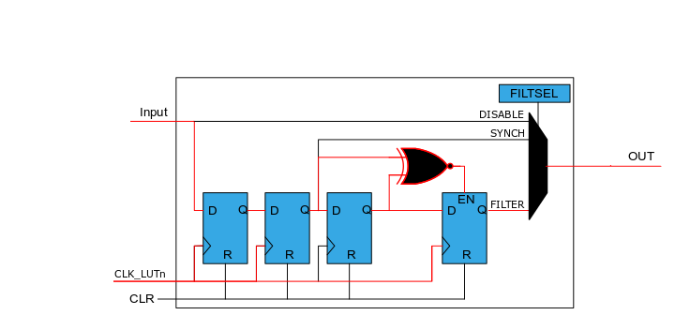

Using LUT feedback feature, a divide by eight configuration is obtained. The signal that will be divided must be used as clock input for the LUT and the output of the LUT must be linked to the input.