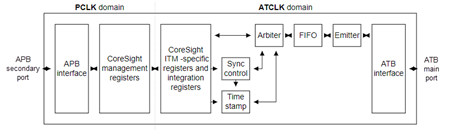

5.4.1 How ITM Trace Works

All SAM MCUs/MPUs that support ITM trace are Arm® Cortex®-M processor-based devices with Arm® CoreSight® architecture. Currently ITM is supported in Cortex M3, M4, M33, and SC300 cores.

The CoreSight Instrumentation Trace Macrocell (ITM) block is a software application driven trace source. Supporting user code generates SoftWare Instrumentation Trace (SWIT). In addition, the block provides a coarse-grained timestamp functionality. The main uses for this block are to:

- support

printfstyle debugging. - trace OS and application events.

- emit diagnostic system information.

MPLAB ICD 5 is capable of streaming UART-format ITM trace to the host computer. Trace is captured on the TRACE/SWO pin of the 10-pin header (JTAG TDO pin). Data is buffered internally on the MPLAB ICD 5 and is sent over the trace interface to the host computer.

The ITM contains the following sub-blocks:

- Timestamp

-

Generates timestamp packet.

- Sync control

-

ITM synchronizer.

- Arbiter

-

Arbitrates between synchronous, timestamp, and SWIT packet.

- FIFO

-

ATB First In First Out (FIFO).

- Emitter

-

ATB registered emitter.

Data is written to the stimulus registers using the APB interface. This data is then transmitted on the ATB interface as SWIT packets .