The DSU implements a feature for automatic testing of memory, also known as MBIST (memory built-in self test). This is primarily intended for production test of on-board memories. MBIST cannot be operated from the external address range when the device is protected by the NVMCTRL security bit. If an MBIST command is issued when the device is protected, a protection error is reported in the Protection Error bit in the Status A register (STATUSA.PERR).

- 1.Algorithm

The algorithm used for testing is a type of March algorithm called "March LR". This algorithm is able to detect a wide range of memory defects, while still keeping a linear run time. The algorithm is:

- a.Write entire memory to '0', in any order.

- b.Bit by bit read '0', write '1', in descending order.

- c.Bit by bit read '1', write '0', read '0', write '1', in ascending order.

- d.Bit by bit read '1', write '0', in ascending order.

- e.Bit by bit read '0', write '1', read '1', write '0', in ascending order.

- f.Read '0' from entire memory, in ascending order.

The specific implementation used as a run time which depends on the CPU clock frequency and the number of bytes tested in the RAM. The detected faults are:

- Address decoder faults

- Stuck-at faults

- Transition faults

- Coupling faults

- Linked Coupling faults

- 2.Starting MBIST

To test a memory, you need to write the start address of the memory to the ADDR.ADDR bit field, and the size of the memory into the Length register.

For best test coverage, an entire physical memory block should be tested at once. It is possible to test only a subset of a memory, but the test coverage will then be somewhat lower.

The actual test is started by writing a '1' to CTRL.MBIST. A running MBIST operation can be canceled by writing a '1' to CTRL.SWRST.

- 3.Interpreting the

Results

The tester should monitor the STATUSA register. When the operation is completed, STATUSA.DONE is set. There are two different modes:

- ADDR.AMOD=0: exit-on-error (default)

In this mode, the algorithm terminates either when a fault is detected or on successful completion. In both cases, STATUSA.DONE is set. If an error was detected, STATUSA.FAIL will be set. User then can read the DATA and ADDR registers to locate the fault.

- ADDR.AMOD=1: pause-on-error

In this mode, the MBIST algorithm is paused when an error is detected. In such a situation, only STATUSA.FAIL is asserted. The state machine waits for user to clear STATUSA.FAIL by writing a '1' in STATUSA.FAIL to resume. Prior to resuming, user can read the DATA and ADDR registers to locate the fault.

- ADDR.AMOD=0: exit-on-error (default)

- 4.Locating Faults

If the test stops with STATUSA.FAIL set, one or more bits failed the test. The test stops at the first detected error. The position of the failing bit can be found by reading the following registers:

- ADDR: Address of the word containing the failing bit

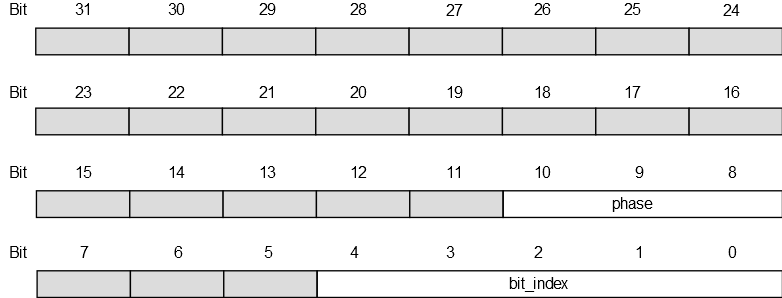

- DATA: contains data to identify which bit failed, and during which phase of the test it failed. The DATA register will in this case contains the following bit groups:

- bit_index: contains the bit number of the failing bit

- phase: indicates which phase of the test failed and the cause of the error, as listed in the following table.

| Phase | Test actions |

|---|---|

| 0 | Write all bits to zero. This phase cannot fail. |

| 1 | Read '0', write '1', increment address |

| 2 | Read '1', write '0' |

| 3 | Read '0', write '1', decrement address |

| 4 | Read '1', write '0', decrement address |

| 5 | Read '0', write '1' |

| 6 | Read '1', write '0', decrement address |

| 7 | Read all zeros. bit_index is not used |

| AMOD[1:0] | Description |

|---|---|

| 0x0 | Exit on Error |

| 0x1 | Pause on Error |

| 0x2, 0x3 | Reserved |