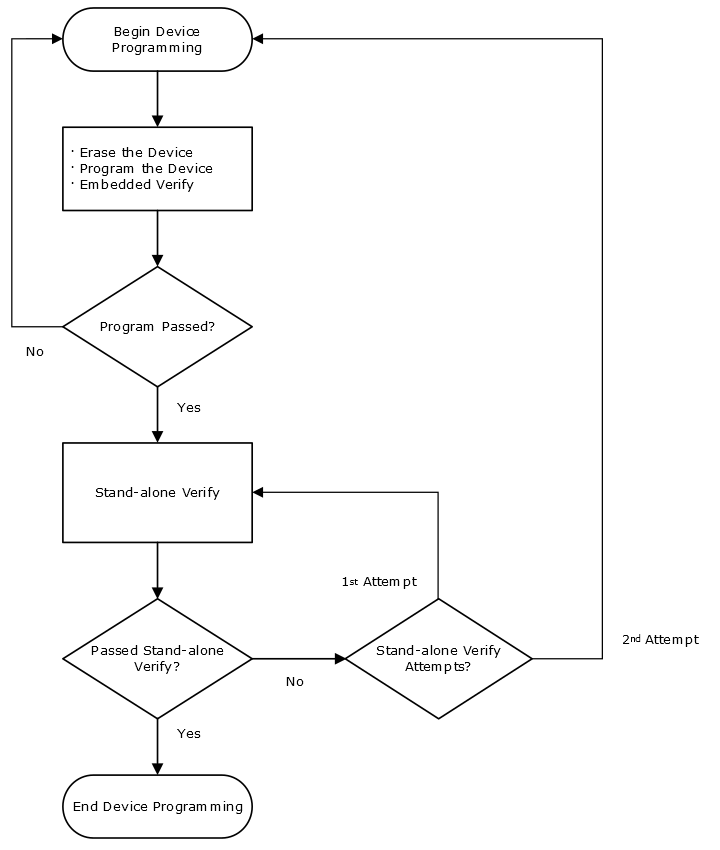

When reprogramming is initiated, the FPGA is erased. Therefore, the programming and stand-alone verify operations must be completed to success, otherwise the FPGA will be inoperable. The following sequence must be followed when performing in-flight reprogramming:

- Programming must be followed by stand-alone verify.

- If programming fails, programming must be attempted again.

- If stand-alone verify fails, the stand-alone verify action must be attempted again.

- If stand-alone verify fails second time, reprogramming of the device must be initiated again.

For information about timing requirements and interface to the RT PolarFire FPGA JTAG pins, see JTAG Programming.

The following figure shows the sequence of in-flight reprogramming.

Figure 1. In-Flight Reprogramming Flow

Chart