| CB | Capacitive load for each bus line | fSCL≤100 kHz | - | - | 400 | pF |

| fSCL≤400 kHz | - | - | 400 |

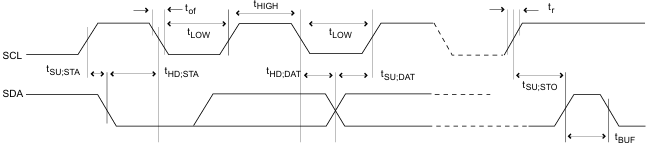

| tR | Rise time for both SDA and SCL | fSCL≤100 kHz | - | - | 1000 | ns |

| fSCL≤400 kHz | 20 | - | 300 | ns |

| tOF | Output fall time from VIHmin to

VILmax | 10 pF < Capacitance of bus line < 400 pF | fSCL≤400 kHz | 20+0.1×CB | - | 300 | ns |

| tSP | Spikes suppressed by Input filter | | 0 | - | 50 | ns |

| tHD;STA | Hold time (repeated) Start condition | fSCL≤100 kHz | 4.0 | - | - | µs |

| fSCL≤400 kHz | 0.6 | - | - |

| tLOW | Low period of SCL Clock | fSCL≤100 kHz | 4.7 | - | - | µs |

| fSCL≤400 kHz | 1.3 | - | - |

| tHIGH | High period of SCL Clock | fSCL≤100 kHz | 4.0 | - | - | µs |

| fSCL≤400 kHz | 0.6 | - | - |

| tSU;STA | Setup time for a repeated Start condition | fSCL≤100 kHz | 4.7 | - | - | µs |

| fSCL≤400 kHz | 0.6 | - | - |

| tHD;DAT | Data hold time | fSCL≤100 kHz | 0 | - | 3.45 | µs |

| fSCL≤400 kHz | 0 | - | 0.9 |

| tSU;DAT | Data setup time | fSCL≤100 kHz | 250 | - | - | ns |

| fSCL≤400 kHz | 100 | - | - |

| tSU;STO | Setup time for Stop condition | fSCL≤100 kHz | 4 | - | - | µs |

| fSCL≤400 kHz | 0.6 | - | - |

| tBUF | Bus free time between a Stop and Start

condition | fSCL≤100 kHz | 4.7 | - | - | µs |

| fSCL≤400 kHz | 1.3 | - | - |