2.1.1 SAM L1x and PIC32CM Lx 32-pin Variants

The 32-pin VQFN and 32-pin TQFP I/O Pinmux of the PIC32CM1216(LE00/LS00)032 and the SAM L10/L11 are almost identical. The following table provides the comparison between the lowest pin count variants of the SAM Lx and the PIC32CM Lx family of devices.

| Pin Name | Peripheral Pads/Instances on the SAM L1x | Peripheral Pads/Instances on the PIC32CM LE00/LS00 | Comments | Extra Peripheral Instances on the SAM L1x | Extra Peripheral Instances on the PIC32CM LE00/LS00 |

|---|---|---|---|---|---|

| PA00 |

EXTINT[0] (EIC) XY[0] (PTC) OA1NEG (OPAMP) SERCOM1/PAD[0] (SERCOM1) TC2/WO[0] (TC2) |

EXTINT[0] (EIC) XY[0] (PTC) OANEG[1] (OPAMP) SERCOM1/PAD[0] (SERCOM1) | PA00 is completely compatible | TC2 | NA |

| PA01 |

EXTINT[1] (EIC) XY[1] (PTC) OA1POS (OPAMP) SERCOM1/PAD[1] (SERCOM1) TC2/WO[1] (TC2) |

EXTINT[1] (EIC) XY[1] (PTC) OAPOS[1] (OPAMP) SERCOM1/PAD[1] (SERCOM1) | PA01 is completely compatible | TC2 | NA |

| PA02 |

EXTINT[2] (EIC) AIN[0] (ADC) XY[2] (PTC) VOUT (DAC) OA0NEG (OPAMP) SERCOM0/PAD[2] (SERCOM0) |

EXTINT[2] (EIC) AIN[0] (ADC) XY[2] (PTC) VOUT0 (DAC) OANEG[0] (OPAMP) SERCOM0/PAD[2] (SERCOM0) | PA02 is completely compatible | NA | NA |

| PA03 |

EXTINT[3] (EIC) VREFA AIN[1] (ADC) XY[3] (PTC) OA2NEG (OPAMP) SERCOM0/PAD[3] (SERCOM0) |

EXTINT[3] (EIC) VREFA AIN[1] (ADC) XY[3] (PTC) OANEG[2] (OPAMP) SERCOM0/PAD[3] (SERCOM0) | PA03 is completely compatible | NA | NA |

| PA04 |

EXTINT[4] (EIC) VREFB AIN[2] (ADC) AIN[0] (AC) OA2OUT (OPAMP) SERCOM0/PAD[0] (SERCOM0) IN[0] (CCL) TC0/WO[0] (TC0) |

EXTINT[4] (EIC) VREFB AIN[2] (ADC) AIN[0] (AC) OAOUT[2] (OPAMP) SERCOM0/PAD[0] (SERCOM0) IN[0] (CCL) | PA04 is completely compatible | TC0 | NA |

| PA05 |

EXTINT[5] (EIC) AIN[3] (ADC) AIN[1] (AC) XY[4] (PTC) OAPOS[2] (OPAMP) SERCOM0/PAD[1] (SERCOM0) IN[1] (CCL) TC0/WO[1] (TC0) |

EXTINT[5] (EIC) AIN[3] (ADC) AIN[1] (AC) XY[4] (PTC) OAPOS[2] (OPAMP) SERCOM0/PAD[1] (SERCOM0) IN[1] (CCL) | PA05 is completely compatible | TC0 | NA |

| PA06 |

EXTINT[6] (EIC) AIN[4] (ADC) AIN[2] (AC) XY[5] (PTC) OA0POS (OPAMP) SERCOM0/PAD[2] (SERCOM0) IN[2] (CCL) TC1/WO[0] (TC1) |

EXTINT[6] (EIC) AIN[4] (ADC) AIN[2] (AC) XY[5] (PTC) OAPOS[0] (OPAMP) SERCOM0/PAD[2] (SERCOM0) IN[2] (CCL) | PA06 is completely compatible | TC1 | NA |

| PA07 |

EXTINT[7] (EIC) AIN[5] (ADC) AIN[3] (AC) OA0OUT (OPAMP) SERCOM0/PAD[3] (SERCOM0) OUT[0] (CCL) TC1/WO[1] (TC1) |

EXTINT[7] (EIC) AIN[5] (ADC) AIN[3] (AC) VOUT1 (DAC) OAOUT[0] (OPAMP) SERCOM0/PAD[3] (SERCOM0) OUT[0] (CCL) | PA07 is completely compatible | TC1 | DAC |

| PA08 |

NMI (EIC) AIN[6] (ADC) XY[6] (PTC) SERCOM1/PAD[0] (SERCOM1) SERCOM2/PAD[0] (SERCOM2) RTC/ IN[0] (RTC/USB/Debug) IN[3] (CCL) |

NMI (EIC) AIN[6] (ADC) XY[6] (PTC) SERCOM1/PAD[0] (SERCOM1) SERCOM2/PAD[0] (SERCOM2) RTC/ IN[0] (RTC/USB/Debug) IN[3] (CCL) | PA08 is completely compatible | NA | NA |

| PA09 |

EXTINT[0] (EIC) AIN[7] (ADC) XY[7] (PTC) SERCOM1/PAD[1] (SERCOM1) SERCOM2/PAD[1] (SERCOM2) RTC/ IN[1] (RTC/USB/Debug) IN[4] (CCL) |

EXTINT[0] (EIC) AIN[7] (ADC) XY[7] (PTC) SERCOM1/PAD[1] (SERCOM1) SERCOM2/PAD[1] (SERCOM2) RTC/ IN[1] (RTC/USB/Debug) IN[4] (CCL) | PA09 is completely compatible | NA | NA |

| PA10 |

EXTINT[1] (EIC) AIN[8] (ADC) XY[8] (PTC) SERCOM1/PAD[2] (SERCOM1) SERCOM2/PAD[2] (SERCOM2) GCLK/ IO[4] (AC/GCLK) IN[5] (CCL) |

EXTINT[1] (EIC) AIN[8] (ADC) XY[8] (PTC) SERCOM1/PAD[2] (SERCOM1) SERCOM2/PAD[2] (SERCOM2) GCLK/ IO[4] (AC/GCLK) IN[5] (CCL) | PA10 is completely compatible | NA | NA |

| VDDPLL/PA11 |

EXTINT[2] (EIC) AIN[9] (ADC) XY[9] (PTC) SERCOM1/PAD[3] (SERCOM1) SERCOM2/PAD[3] (SERCOM2) GCLK_IO[3] (AC/GCLK) OUT[1] (CCL) | NA | PA11 is not completely compatible |

EIC, ADC, PTC, SERCOM1, SERCOM2, AC/GCLK, CCL | NA |

| PA14/XIN |

EXTINT[3] (EIC) XY[10] (PTC) SERCOM2/PAD[2] (SERCOM2) SERCOM0/PAD[2] (SERCOM0) TC0/ WO[0] (TC0) GCLK/ IO[0] (AC/GCLK) |

EXTINT[3] (EIC) XY[10] (PTC) SERCOM2/PAD[2] (SERCOM2) SERCOM0/PAD[2] (SERCOM0) TC0/ WO[0] (TC0) GCLK/ IO[0] (AC/GCLK) | PA14 is completely compatible | NA | NA |

| PA15/XOUT |

EXTINT[4] (EIC) XY[11] (PTC) SERCOM2/PAD[3] (SERCOM2) SERCOM0/PAD[3] (SERCOM0) TC0/ WO[1] (TC0) GCLK/ IO[1] (AC/GCLK) |

EXTINT[4] (EIC) XY[11] (PTC) SERCOM2/PAD[3] (SERCOM2) SERCOM0/PAD[3] (SERCOM0) TC0/ WO[1] (TC0) GCLK/ IO[1] (AC/GCLK) | PA15 is completely compatible | NA | NA |

| PA16 |

EXTINT[5] (EIC) XY[12] (PTC) SERCOM1/PAD[0] (SERCOM1) SERCOM0/PAD[0] (SERCOM0) RTC/ IN[2] (RTC/USB/Debug) GCLK/ IO[2] (AC/GCLK) IN[0] (CCL) |

EXTINT[5] (EIC) XY[12] (PTC) SERCOM1/PAD[0] (SERCOM1) SERCOM0/PAD[0] (SERCOM0) RTC/ IN[2] (RTC/USB/Debug) GCLK/ IO[2] (AC/GCLK) IN[0] (CCL) | PA16 is completely compatible | NA | NA |

| PA17 |

EXTINT[6] (EIC) XY[13] (PTC) SERCOM1/PAD[1] (SERCOM1) SERCOM0/PAD[1] (SERCOM0) RTC/ IN[3] (RTC/USB/Debug) GCLK/ IO[3] (AC/GCLK) IN[1] (CCL) |

EXTINT[6] (EIC) XY[13] (PTC) SERCOM1/PAD[1] (SERCOM1) SERCOM0/PAD[1] (SERCOM0) RTC/ IN[3] (RTC/USB/Debug) GCLK/ IO[3] (AC/GCLK) IN[1] (CCL) | PA17 is completely compatible | NA | NA |

| PA18 |

EXTINT[7] (EIC) XY[14] (PTC) SERCOM1/PAD[2] (SERCOM1) SERCOM0/PAD[2] (SERCOM0) TC2/ WO[0] (TC2) RTC/ OUT[0] (RTC/USB/Debug) AC/ CMP[0] (AC/GCLK) IN[2] (CCL) |

EXTINT[7] (EIC) XY[14] (PTC) SERCOM1/PAD[2] (SERCOM1) SERCOM0/PAD[2] (SERCOM0) TC2/ WO[0] (TC2) RTC/ OUT[0] (RTC/USB/Debug) AC/ CMP[0] (AC/GCLK) IN[2] (CCL) | PA18 is completely compatible | NA | NA |

| PA19 |

EXTINT[0] (EIC) XY[15] (PTC) SERCOM1/PAD[3] (SERCOM1) SERCOM0/PAD[3] (SERCOM0) TC2/ WO[1] (TC2) RTC/ OUT[1] (RTC/USB/Debug) AC/ CMP[1] (AC/GCLK) OUT[0] (CCL) |

EXTINT[0] (EIC) XY[15] (PTC) SERCOM1/PAD[3] (SERCOM1) SERCOM0/PAD[3] (SERCOM0) TC2/ WO[1] (TC2) RTC/ OUT[1] (RTC/USB/Debug) AC/ CMP[1] (AC/GCLK) OUT[0] (CCL) | PA19 is completely compatible | NA | NA |

| PA22 |

EXTINT[1] (EIC) XY[16] (PTC) SERCOM0/PAD[0] (SERCOM0) SERCOM2/PAD[0] (SERCOM2) TC0/ WO[0] (TC0) RTC/ OUT[2] (RTC/USB/Debug) GCLK/ IO[2] (AC/GCLK) |

EXTINT[1] (EIC) XY[16] (PTC) SERCOM0/PAD[0] (SERCOM0) SERCOM2/PAD[0] (SERCOM2) TC0/ WO[0] (TC0) RTC/ OUT[2] (RTC/USB/Debug) GCLK/ IO[2] (AC/GCLK) | PA22 is completely compatible | NA | NA |

| PA23 |

EXTINT[2] (EIC) XY[17] (PTC) SERCOM0/PAD[1] (SERCOM0) SERCOM2/PAD[1] (SERCOM2) TC0/ WO[1] (TC0) RTC/ OUT[3] (RTC/USB/Debug) GCLK/ IO[1] (AC/GCLK) |

EXTINT[2] (EIC) XY[17] (PTC) SERCOM0/PAD[1] (SERCOM0) SERCOM2/PAD[1] (SERCOM2) TC0/ WO[1] (TC0) RTC/ OUT[3] (RTC/USB/Debug) GCLK/ IO[1] (AC/GCLK) | PA23 is completely compatible | NA | NA |

| PA24 |

EXTINT[3] (EIC) SERCOM0/PAD[2] (SERCOM0) SERCOM2/PAD[2] (SERCOM2) TC1/ WO[0] (TC1) |

EXTINT[3] (EIC) SERCOM0/PAD[2] (SERCOM0) SERCOM2/PAD[2] (SERCOM2) TC1/ WO[0] (TC1) USB/ DM (RTC/USB/Debug) | PA24 is completely compatible | NA | USB |

| PA25 |

EXTINT[4] (EIC) SERCOM0/PAD[3] (SERCOM0) SERCOM2/PAD[3] (SERCOM2) TC1/ WO[1] (TC1) |

EXTINT[4] (EIC) SERCOM0/PAD[3] (SERCOM0) SERCOM2/PAD[3] (SERCOM2) TC1/ WO[1] (TC1) USB/ DP (RTC/USB/Debug) | PA25 is completely compatible | NA | USB |

| PA27 |

EXTINT[5] (EIC) GCLK_IO[0] (AC/GCLK) | NA | PA27 is not completely compatible | EIC, GCLK | NA |

| PA30 |

EXTINT[6] (EIC) XY[18] (PTC) SERCOM1/PAD[2] (SERCOM1) SWCLK GCLK/ IO[0] (AC/GCLK) IN[3] (CCL) TC1/WO[0] (TC1) |

EXTINT[6] (EIC) XY[18] (PTC) SERCOM1/PAD[2] (SERCOM1) SWCLK GCLK/ IO[0] (AC/GCLK) IN[3] (CCL) | PA30 is completely compatible | TC1 | NA |

| PA31 |

EXTINT[7] (EIC) XY[19] (PTC) SERCOM1/PAD[3] (SERCOM1) OUT[1] (CCL) TC1/WO[1] (TC1) |

EXTINT[7] (EIC) XY[19] (PTC) SERCOM1/PAD[3] (SERCOM1) OUT[1] (CCL) | PA31 is completely compatible | TC1 | NA |

Differences:

- The SAM L10/L11 can be configured with TC2/WO[0], TC2/WO[1] pads on the PA00/XIN32 and PA01/XOUT32 pins while the PIC32CM LE00 and LS00 do not have TC2 peripheral on these pins.

- The SAM L10/L11 can be configured with TC0/WO[0], TC0/WO[1] pads on the PA04 and PA05 pins while the PIC32CM LE00 and LS00 do not have TC0 peripheral on these pins.

- The SAM L10/L11 can be configured with TC1/WO[0], TC1/WO[1] pads on the PA06 and PA07 pins while the PIC32CM LE00 and LS00 do not have TC1 peripheral on these pins.

- The PIC32CM LE00 and LS00 have USB/DM interface on the PA24 pin while the SAM L10 and L11 do not have this interface.

- The PIC32CM LE00 and LS00 have USB/DP interface on the PA25 pin while the SAM L10 and L11 do not have this interface.

- The SAM L10/L11 can be configured with TC1/WO[0], TC1/WO[1] pads on the PA30 and PA31 pins while the PIC32CM LE00 and LS00 do not have TC1 peripheral on these pins.

- The PA11 pin on the SAM L1x can be configured as any other normal pin (it has EXTINT[2] > EIC instance, AIN[9] > ADC instance , XY[9] > PTC instance, SERCOM1/PAD[3], SERCOM2/PAD[3], GCLK_IO[3] > GCLK instance, OUT[1] > CCL instance) but on the PIC32CM Lx, it is dedicated to the VDDPLL supply.

- The PA27 pin on the SAM L1x can be

configured as any other normal pin but on the PIC32CM Lx, it is dedicated to

VSS.

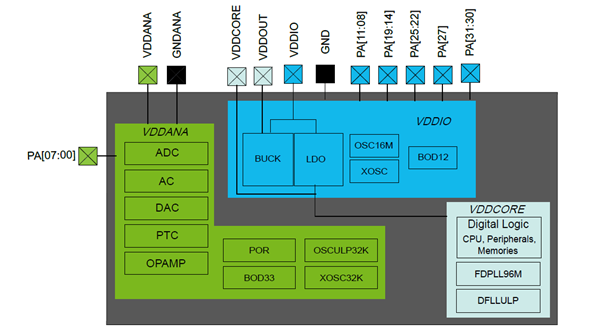

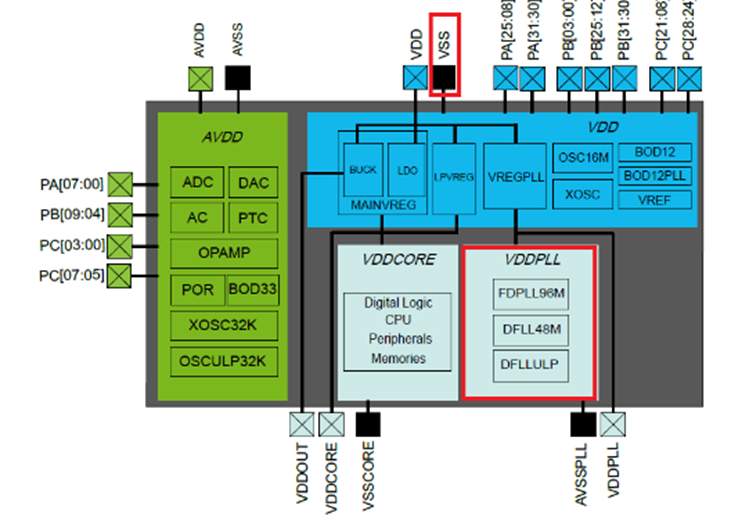

The following figures show the power supply block diagrams of the SAM L1x and PIC32CM Lx MCUs. The highlighted block in the Figure 2-1 indicates that VDDPLL is a separate block within the PIC32CM Lx MCUs, which accounts for the last two points.

Figure 2-1. PIC32CM Lx Block Diagram

Figure 2-2. SAM L1x Block Diagram