4 Universal Serial Interface

The Universal Serial Interface provides the basic hardware resources needed for synchronous serial communication. The main features of the USI are:

- Two-wire Synchronous Data Transfer

- Three-wire Synchronous Data Transfer

- Data Received Interrupt

- Wake-up from Idle Mode

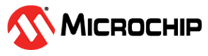

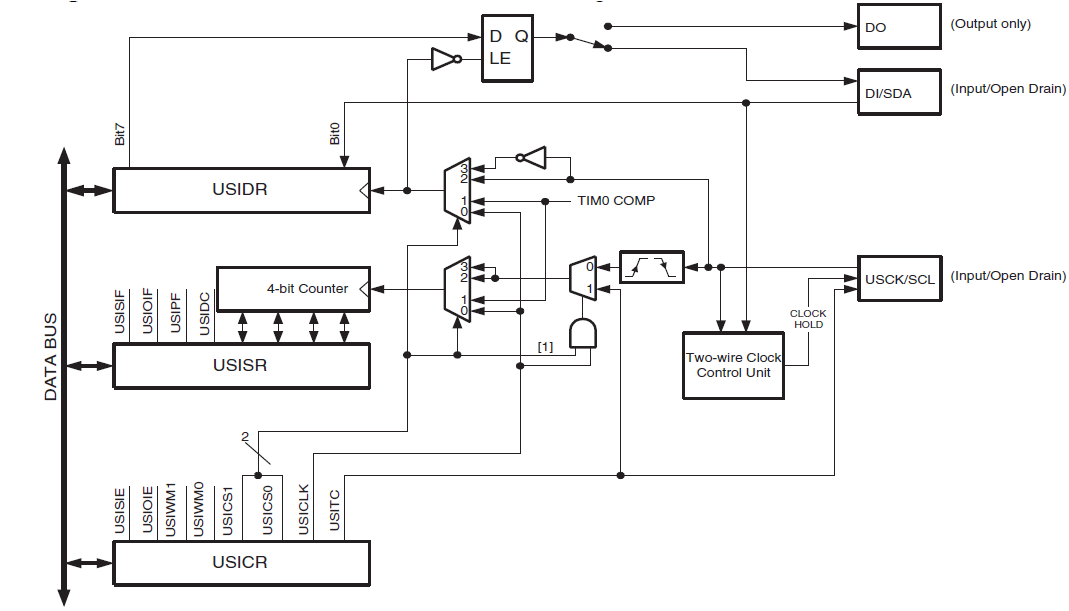

The USI Three-wire mode is compliant with the Serial Peripheral Interface (SPI) Mode 0 and 1, but does not have the Slave Select (SS) pin functionality. However, this feature can be implemented in software if necessary. The first figure below shows the USI module block diagram, and the second figure below shows the module in Three-wire mode.

The USI Data Register (USIDR) is an 8-bit Shift Register that contains the incoming and outgoing data. The register has no buffering so the data must be read as quickly as possible to ensure that no data is lost. The USI Status Register (USISR) contains a 4-bit counter. Both the shift register and the counter are clocked simultaneously by the same clock source. This allows the counter to count the number of bits received or transmitted and sets a flag, alternatively generates an interrupt, when the transfer is complete. The clock can be selected to use three different sources; The USCK pin, Timer/Counter0 Compare Match, or from software.

The figure above shows two USI units operating in Three-wire mode, one as Master and one as Slave. The two shift registers are interconnected in such way that after eight USCK clocks, the data in each register are interchanged. The same clock also increments the USI's 4-bit counter. The Counter Overflow Interrupt Flag, or USIOIF, can therefore be used to determine when a transfer is completed. The clock is generated by the Master device software by toggling the USCK pin via the PORT Register or by writing a one to the USITC bit in USICR.

It is the master device’s responsibility to give the slave device time to prepare its next byte before starting a new transfer.