2 Serial Peripheral Interface

The Serial Peripheral Interface allows high-speed synchronous data transfer between an AVR device and peripheral devices, or between several AVR devices.

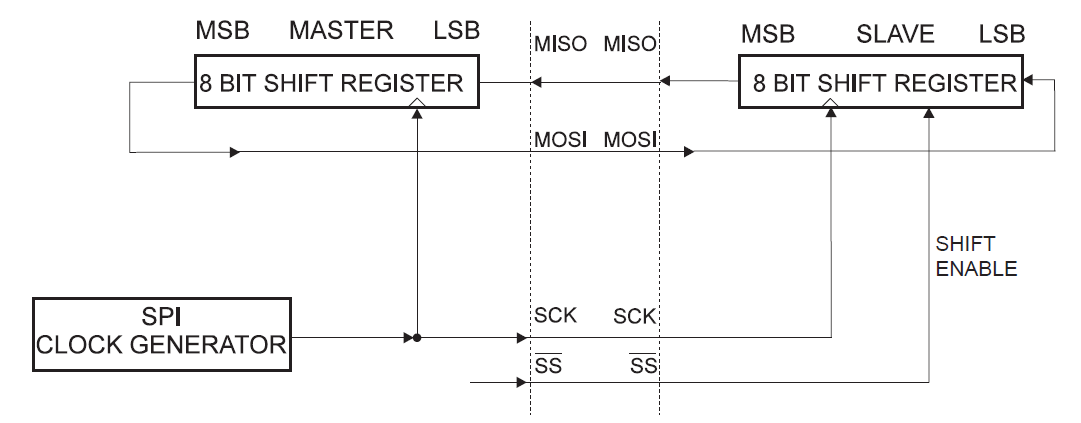

The interconnection between Master and Slave devices with SPI is shown in the figure below. The system consists of two shift registers and a master clock generator. The SPI Master initiates the communication cycle when pulling low the Slave Select (SS) pin of the desired Slave. Master and Slave prepare the data to be sent in their respective shift registers, and the Master generates the required clock pulses on the SCK line to interchange data.