3.1 MCC Configuration

- Clock Control configuration:

- Clock Source: HFINTOSC

- HF Internal Clock: 64 MHz

- ADCRC Oscillator: Enabled

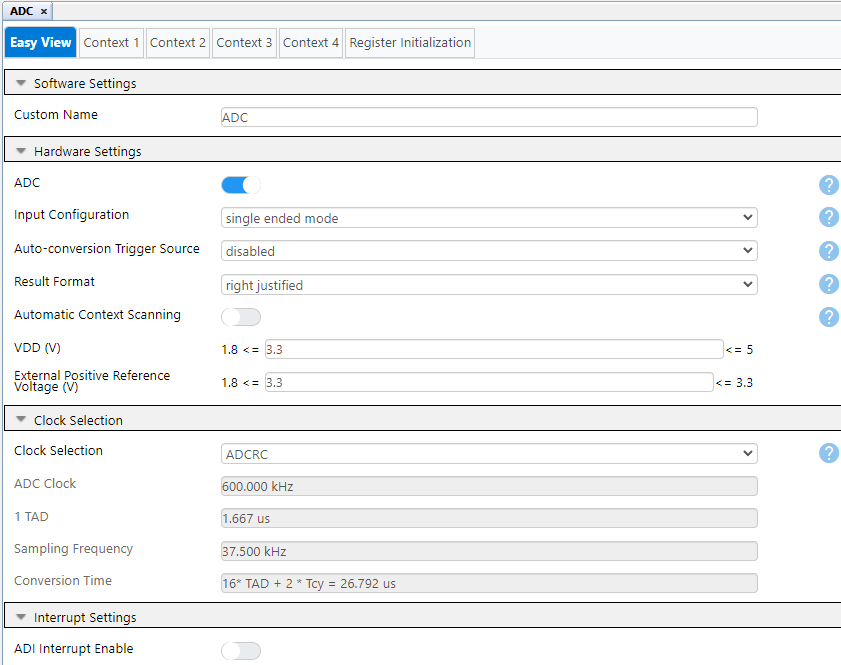

- ADC configuration:

- Input Configuration: Single-Ended mode

- Result Format: Right justified

- VDD: 3.3V

- Clock Selection: ADCRC

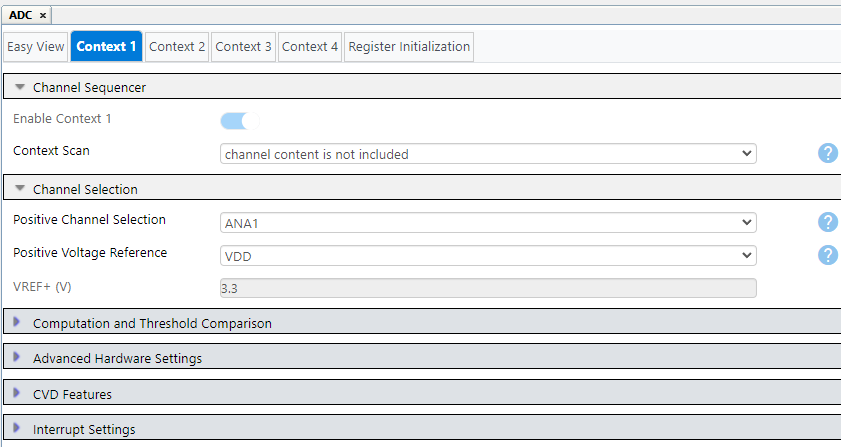

- ADC Context 1 tab:

- Positive Channel Selection: ANA1

- Positive Voltage Reference: VDD

- Operating Mode Selection: Average mode

- Error Calculation mode: First derivative of single measurement

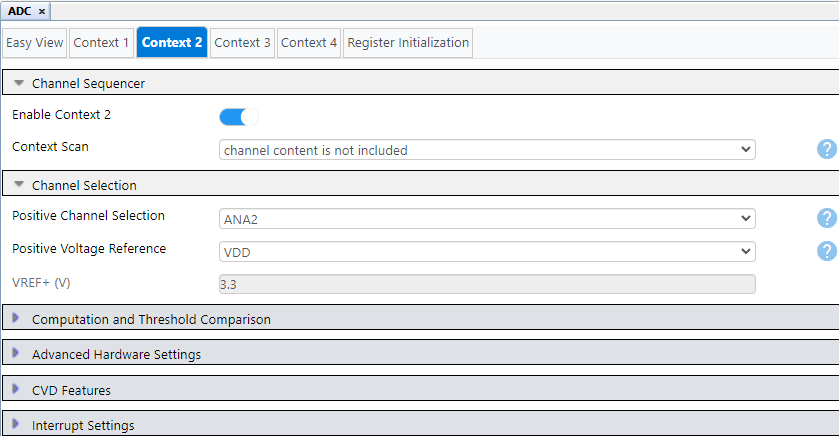

- ADC Context 2 tab:

- Positive Channel Selection: ANA2

- Positive Voltage Reference: VDD

- Operating Mode Selection: Basic mode

- Error Calculation mode: First derivative of single measurement

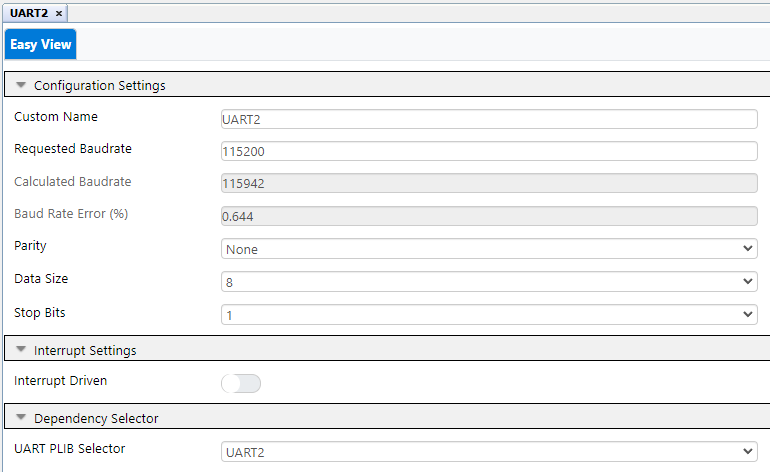

- UART2:

- 115200 baud rate

- Eight data bits

- No parity bit

- One stop bit

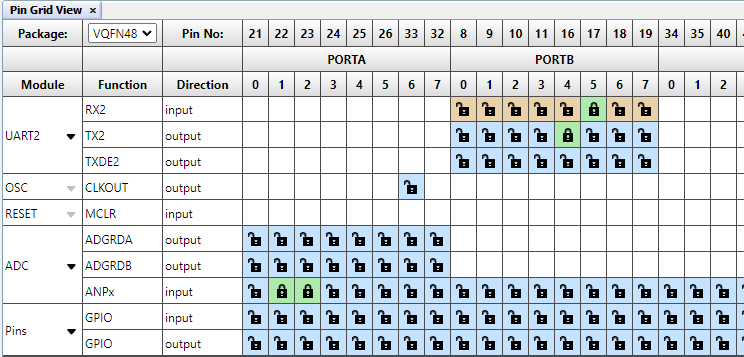

- Pins configuration

Note: For this example, configure the following settings on the

terminal software: Baud rate = 115200, 8-bit data size, one stop bit, no parity

bit.