1.5 CLC Manchester Encoder

This example application shows how to use the CLC peripheral library and generate a Manchester-encoded output.

Description

This demonstrates a way to generate a Manchester-encoded output using a SPI port and the CLC. The SPI port is sending out a predefined buffer of data in a circular fashion. Data is sent out LSB first, with CLCOUT being the Manchester-encoded output. Pins are configured such that a logic analyzer can be attached to see the input (MOSI and REFCLKO) and the output (CLCOUT) simultaneously.

Downloading and building the application

To clone or download this application from Github, go to the main page of this repository and then click Clone button to clone this repository or download as zip file. This content can also be downloaded using content manager by following these instructions.

Path of the application within the repository is apps/clc/manchester_encoder/firmware.

To build the application, refer to the following table and open the project using its IDE.

| Project Name | Description |

|---|---|

| pic32mm_usb_curiosity.X | MPLABX project for PIC32MM USB Curiosity board |

Setting up the hardware

The following table shows the target hardware for the application projects.

| Project Name | Description |

|---|---|

| pic32mm_usb_curiosity.X | PIC32MM USB Curiosity board |

Setting up PIC32MM USB Curiosity Board

- RB15 (on mikroBUS socket J4) has REFCLKO output, which is internally connected to CLC

- RD0 (pin 5 on J10) has MOSI output, which is internally connected to CLC

- RB0 (on mikroBUS socket J12) has CLC output (CLC1OUT)

- Connect the Debug USB port on the board to the computer using a micro USB cable

Running the Application

- Connect a logic analyzer to MOSI pin

- Connect a logic analyzer to REFCLKO pin

- Connect a logic analyzer to the Manchester-encoded output CLC1OUT pin

- Refer to the following table for pin details:

Board MOSI pin REFCLKO pin CLCOUT pin PIC32MM USB Curiosity board RD0 (pin 5 on J10) RB15 (on mikroBUS socket J4) RB0 (on mikroBUS socket J12) - Build and Program the application using its IDE

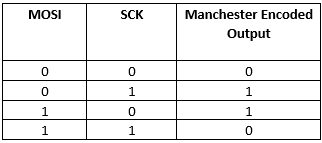

- Observe the output on logic analyzer, it should follow the truth table as shown

in the following diagram: