3.1 USART Registers Configuration

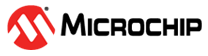

- Set Control Register C

(USART_CTRLC).

- Bit

7:6 – CMODE[1:0]: USART Communication Mode

Select Master SPI communication mode provided with a synchronous clock and data output.

- Bit 5:4 – PMODE[1:0]: Parity Mode

- Bit 3 – SBMODE: Stop Bit Mode

- Bit 2

– UDORD: Data Order

This bit selects either LSB or MSB of the data to be transmitted first. Default is used here.

- Bit 1

– UCPHA: Clock Phase

This bit determines if data is sampled on the trailing edge of XCK.

- Bit

7:6 – CMODE[1:0]: USART Communication Mode

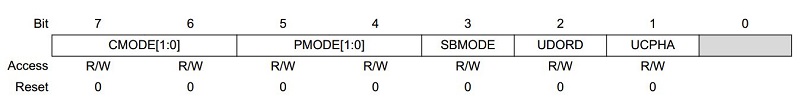

- Set Baud Register

(USART_BAUD).

- Bit

15:0 – BAUD[15:0]: USART Baud Rate

For Master SPI mode, only ten MSBs are valid. The calculation equations are described in the data sheet.

- Bit

15:0 – BAUD[15:0]: USART Baud Rate

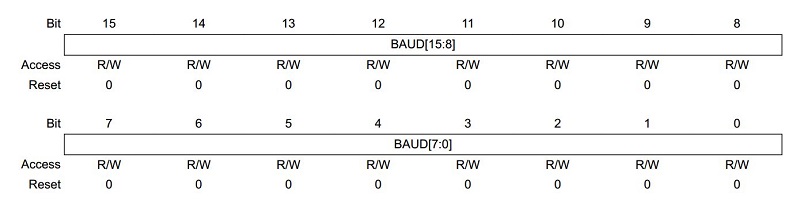

- Set Control Register A

(USART_CTRLA).

- Bit 7 – RXCIE: Receive Complete Interrupt Enable

- Bit 6 – TXCIE: Transmit Complete Interrupt Enable

- Bit 5

– DREIE: Data Register Empty Interrupt

Enable

Set this interrupt to enable for data sending.

- Bit 4 – RXSIE: Receiver Start Frame Interrupt Enable

- Bit 3 – LBME: Loop-back Mode Enable

- Bit 2 – ABEIE: Auto-baud Error Interrupt Enable

- Bits 1:0 – RS485[1:0]: RS485 Mode

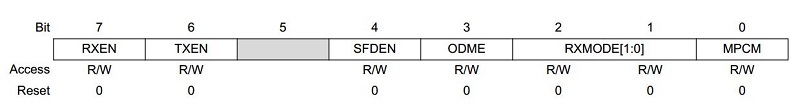

- Set Control Register B

(USART_CTRLB).

- Bit 7 – RXEN: Receiver Enable

- Bit 6

– TXEN: Transmitter Enable

Set to enable USART transmitter.

- Bit 4 – SFDEN: Start Frame Detection Enable

- Bit 3 – ODME: Open Drain Mode Enable

- Bits 2:1 – RXMODE[1:0]: Receiver Mode

- Bit 0 – MPCM: Multiprocessor Communication Mode