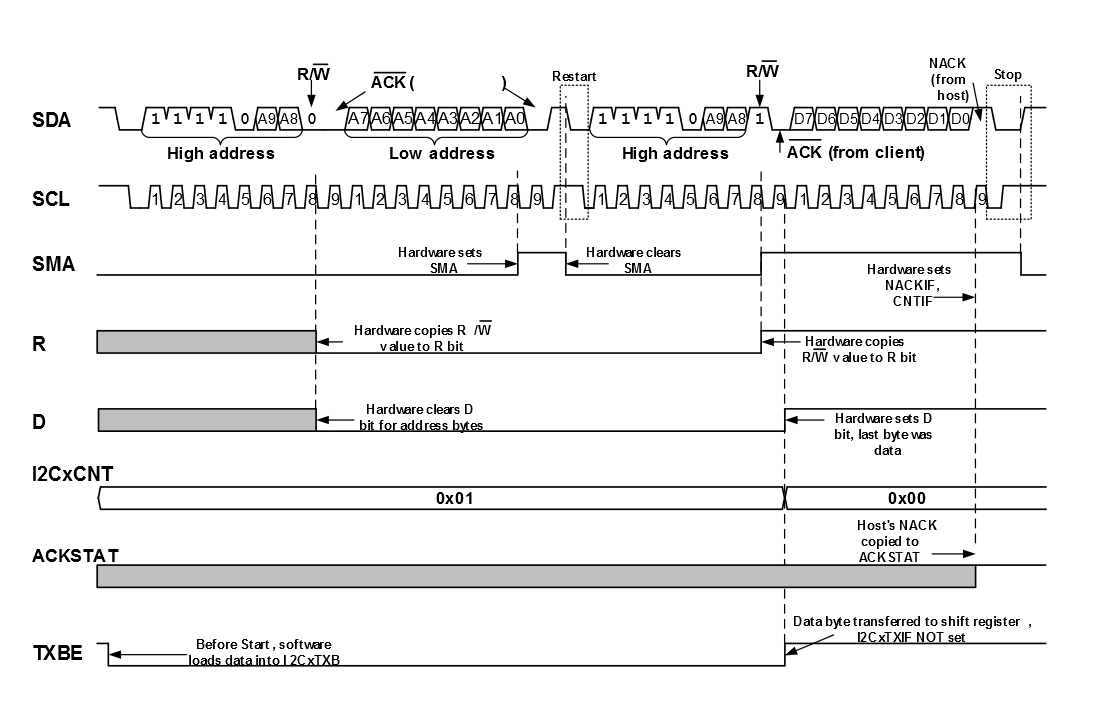

37.4.1.4.1 Client Transmission (10-Bit Addressing Mode)

The following section describes the sequence of events that occur when the module is transmitting data in 10-bit Addressing mode:

- The host device issues a Start condition. Once the Start condition has been detected, client hardware sets the Start Condition Interrupt Flag (SCIF) bit. If the Start Condition Interrupt Enable (SCIE) bit is also set, the generic I2CxIF is also set.

- Host hardware transmits the 10-bit

high address byte with the R/W bit clear

(R/W =

0). - Client hardware compares the received

address to the values in the I2CxADR registers. If the client is configured in

10-bit Addressing mode (no masking), the received high address byte is compared to

the values in I2CxADR1 and I2CxADR3. In 10-bit Addressing with Masking mode, the

received high address byte is compared to the masked value of I2CxADR1.

If an address match occurs:

- The R/W value is copied to the Read Information (R) bit by module hardware.

- The Data (D) bit is cleared by hardware.

- The Address Interrupt Flag

(ADRIF) bit is set (ADRIF =

1). - The matching address is

loaded into either the I2CxADB1 register or into the I2CxRXB register as determined by the Address Buffer Disable

(ABD) bit. When ABD is clear (ABD =

0), the matching address is copied to I2CxADB1. When ABD is set (ABD =1), the matching address is copied to I2CxRXB, which also sets the Receive Buffer Full Status (RXBF) bit and the I2C Receive Interrupt Flag (I2CxRXIF) bit.

Important: Regardless of whether the Address Interrupt and Hold Enable (ADRIE) bit is set, clock stretching does not occur when the R/W bit is clear in 10-bit Addressing modes.If no address match occurs, the module remains Idle.

- The host device transmits the 9th

clock pulse, and client hardware transfers the value of the ACKDT bit onto the SDA line. If there are pending errors,

such as a receive buffer overflow (RXO =

1), client hardware generates a NACK and the module goes Idle. - The host device transmits the low

address byte. If the client is configured in 10-bit Addressing mode (no masking),

the received low address byte is compared to the values in I2CxADR0

and I2CxADR2. In 10-bit Addressing with Masking mode, the received low

address byte is compared to the masked value of I2CxADR0.

If a match occurs:

- The Client Mode Active (SMA) bit is set by module hardware.

- ADRIF is set. If ADRIE is set and the Clock Stretching Disable (CSD) bit is clear, hardware sets the Client Clock Stretching (CSTR) bit and the generic I2CxIF bit. This allows time for the client to read either I2CxADB0 or I2CxRXB and selectively ACK/NACK based on the received address. When the client has finished processing the address, software must clear CSTR to resume operation.

- The matching received address

is loaded into either the I2CxADB0 register or into the I2CxRXB register as determined by the ABD bit. When ABD is clear (ABD =

0), the matching address is copied to I2CxADB0. When ABD is set (ABD =1), the matching address is copied to I2CxRXB, which also sets RXBF and I2CxRXIF. I2CxRXIF is a read-only bit, and must be cleared by either reading I2CxRXB or by setting the Clear Buffer (CLRBF) bit (CLRBF =1).

If no match occurs, the module goes Idle.

- The host device transmits the 9th

clock pulse, and client hardware transfers the value of the ACKDT bit onto the SDA line. If there are pending errors,

such as a receive buffer overflow (RXO =

1), client hardware generates a NACK and the module goes Idle. - After the 9th falling edge of SCL,

the Acknowledge Status Time Interrupt Flag (ACKTIF) bit is set. If the Acknowledge Time Interrupt and

Hold Enable (ACKTIE) bit is also set, the generic I2CxIF is set, and if

client hardware generated an ACK, the CSTR bit is also set and the clock is stretched (when CSD =

0). If a NACK was generated, the CSTR bit remains unchanged. Once completed, software must clear CSTR and ACKTIF to release the clock and resume operation. - Host hardware issues a Restart condition (cannot be a Start condition), and once the client detects the Restart, hardware sets the Restart Condition Interrupt Flag (RSCIF). If the Restart Condition Interrupt Enable (RSCIE) bit is also set, the generic I2CxIF is also set.

- Host hardware transmits the client’s

high address byte with R/W set.

If the received high address byte matches:

- The R/W bit value is copied to the R bit.

- The SMA bit is set.

- The D bit is cleared, indicating the last byte as an address.

- ADRIF is set. If ADRIE is set, and the CSD bit is clear, hardware sets CSTR and the generic I2CxIF bit. This allows time for the client to read either I2CxADB1 or I2CxRXB and selectively ACK/NACK based on the received address. When the client has finished processing the address, software must clear CSTR to resume operation.

- The matching received address

is loaded into either the I2CxADB1 register or into the I2CxRXB register as determined by the ABD bit. When ABD is clear (ABD =

0), the matching address is copied to I2CxADB1. When ABD is set (ABD =1), the matching address is copied to I2CxRXB, which also sets RXBF and I2CxRXIF. I2CxRXIF is a read-only bit, and must be cleared by either reading I2CxRXB or by setting CLRBF (CLRBF =1).

If the address does not match, the module goes Idle.

- If the Transmit Buffer Empty Status

(TXBE) bit is set (TXBE =

1), I2CxCNT has a nonzero value (I2CxCNT !=0), and the I2C Transmit Interrupt Flag (I2CxTXIF) is set (I2CxTXIF =1), client hardware sets CSTR, stretches the clock (when CSD =0), and waits for software to load I2CxTXB with data. I2CxTXB must be loaded to clear I2CxTXIF. Once data is loaded into I2CxTXB, hardware automatically clears CSTR to resume communication. - The host device transmits the 9th

clock pulse, and client hardware transfers the value of the ACKDT bit onto the SDA line. If there are pending errors,

such as a receive overflow (RXO =

1), client hardware automatically generates a NACK condition. NACKIF is set, and the module goes Idle. - Upon the 9th falling SCL edge, the

data byte in I2CxTXB is transferred to the transmit shift register, and I2CxCNT is

decremented by one. Additionally, the ACKTIF bit is set. If the ACKTIE bit is also set, the generic I2CxIF is set, and if

client hardware generated an ACK, the CSTR bit is also set and the clock is stretched (when CSD =

0). If a NACK was generated, the CSTR bit remains unchanged. Once complete, software must clear CSTR and ACKTIF to release the clock and continue operation. - If the client generated an ACK and I2CxCNT is nonzero, host hardware transmits eight clock pulses, and client hardware begins to shift the data byte out of the shift register starting with the Most Significant bit (MSb).

- After the 8th falling edge of SCL,

client hardware checks the status of TXBE and I2CxCNT.

If TXBE is set and I2CxCNT has a nonzero count value, hardware sets CSTR and the clock is stretched (when CSD =

0) until software loads I2CxTXB with new data. Once I2CxTXB has been loaded, hardware clears CSTR to resume communication. - Once the host hardware clocks in all

eight data bits, it transmits the 9th clock pulse along with the

ACK/NACK response back to the client. Client hardware

copies the ACK/NACK value to the Acknowledge Status (ACKSTAT) bit and sets ACKTIF. If ACKTIE is also set, client hardware sets the generic I2CxIF

bit and CSTR, and stretches the clock (when CSD =

0). Software must clear CSTR to resume operation. - After the 9th falling edge of SCL,

data currently loaded in I2CxTXB is transferred to the transmit shift

register, setting both TXBE and I2CxTXIF. I2CxCNT is decremented by one. If I2CxCNT is zero (I2CxCNT =

0), CNTIF is set. - If I2CxCNT is

nonzero and the host issued an ACK on the last byte (ACKSTAT =

0), the host transmits eight clock pulses, and client hardware begins to shift data out of the shift register. - Repeat steps 13-17 until the host has

received all the requested data (I2CxCNT =

0). Once all data is received, host hardware transmits a NACK condition, followed by either a Stop or Restart condition. Once the NACK has been received by the client, hardware sets NACKIF and clears SMA. If the NACK Detect Interrupt Enable (NACKIE) bit is also set, the generic I2C Error Interrupt Flag (I2CxEIF) is set. If the host issued a Stop condition, client hardware sets the Stop Condition Interrupt Flag (PCIF). If the host issued a Restart condition, client hardware sets the Restart Condition Interrupt Flag (RSCIF) bit. If the associated interrupt enable bits are also set, the generic I2CxIF is also set.