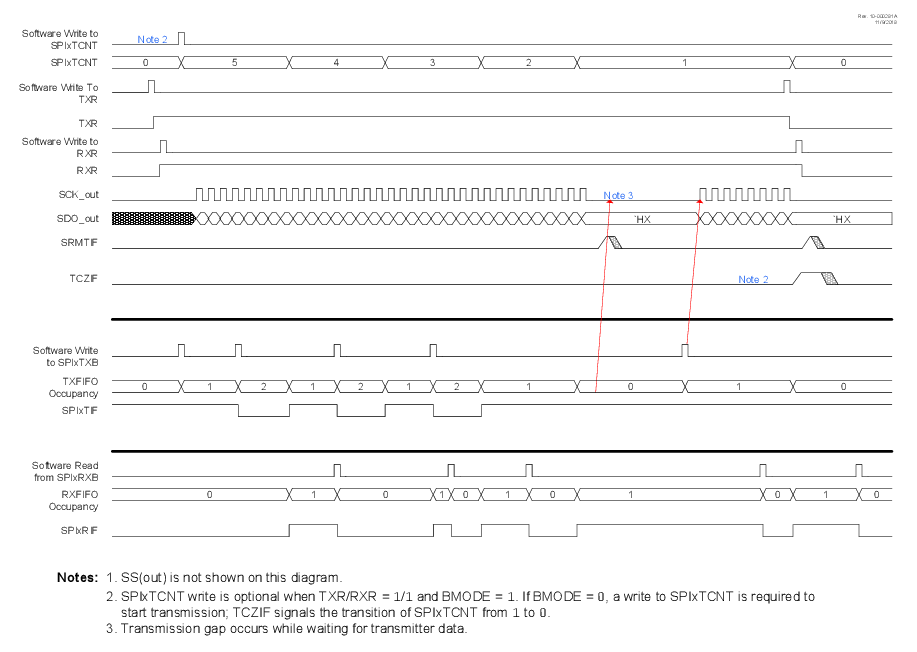

36.3.1 Full Duplex Mode

When BMODE = 1, data transfers will occur whenever the receive FIFO is

not full and data is present in the transmit FIFO. In practice, as long as the receive

FIFO is not full, data will be transmitted/received as soon as the SPIxTXB register is

written to, matching the functionality of SPI (MSSP) modules on older 8-bit Microchip

devices. The SPIxTCNT will decrement with each transfer. However, when SPIxTCNT is zero,

the next transfer is not inhibited and the corresponding SPIxTCNT decrement will cause

the count to roll over to the maximum value. The following figure shows an example of a

communication using this mode.

1, TXR = 1

When BMODE = 0, the transfer counter (SPIxTCNT) must also be written to

before transfers will occur. Transfers will cease when the transfer counter reaches

‘0’. For example, if SPIxTXB is written twice and then SPIxTCNTL is

written with ‘3’, the transfer will start with the SPIxTCNTL write. The

two bytes in the TXFIFO will be sent after which the transfer will suspend until the

third and last byte is written to SPIxTXB.