2.1.2 Read Memory Transfer

The data of the serial memory is accessed by sending an instruction with QSPI_IFR.DATAEN = 1 and QSPI_IFR.TFRTYP = 1. In this mode, the QSPI is able to read data at random address into the serial Flash memory, allowing the CPU to execute code directly from it (XIP). In order to fetch data, the user must first configure the instruction frame by writing the QSPI_IFR. Then data can be read at any address in the QSPI address space mapping. The address of the system bus read accesses matches the address of the data inside the serial Flash memory.

In Serial Memory mode, QSPI is compatible with four protocols:

- Single-Bit SPI: Communicate with external memory with QIO0.

- Dual SPI: Communicate with external memory with QIO0 and QIO1.

- Quad SPI: Communicate with external memory with QIO0, QIO1, QIO2 and QIO3.

- Octal SPI protocols: Communicate with external memory with QIO0 to QIO7.

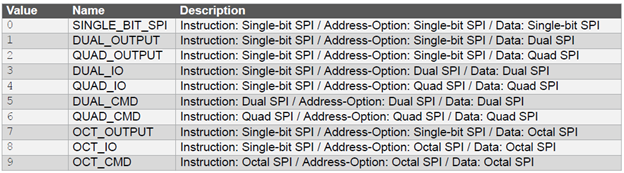

When communicating with external memory, the instruction, address, and data can be set to use different modes which are configured in the Instruction Frame register (QSPI_IFR). There are ten combinations:

For detailed information on how to transfer instruction, address, and data with external memory, refer to the respective product data sheet.