41.4.9.1 CVD Operation

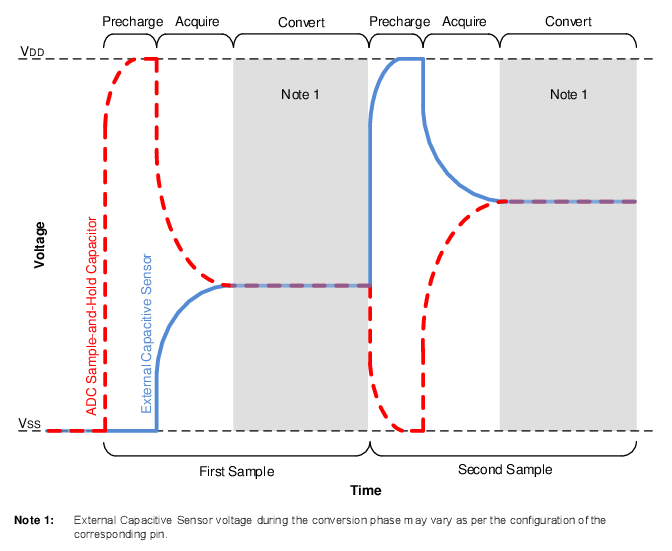

A CVD operation begins with the ADC’s internal Sample-and-Hold capacitor (CHOLD) being disconnected from the path, which connects it to the external capacitive sensor node. While disconnected, CHOLD is precharged to VDD or discharged to VSS. If the PCSC bit is clear, the sensor node is either discharged or charged to VSS or VDD, respectively, to the opposite level of CHOLD. If PCSC is set, the external capacitive sensor node receives no precharge. When the precharge phase is complete, the VDD/VSS bias paths for the two nodes are disconnected and the paths between CHOLD and the external sensor node is reconnected, at which time the acquisition phase of the CVD operation begins. During acquisition, a capacitive voltage divider is formed between the precharged CHOLD and sensor nodes, resulting in a final voltage level setting on CHOLD, which is determined by the capacitances and precharge levels of the two nodes. After acquisition, the ADC converts the voltage level on CHOLD. This process is then repeated with the selected precharge levels inverted for both the CHOLD and the sensor nodes. The waveform for two CVD measurements, which is known as differential CVD measurement, is shown in the following figure.