5.5 Clock Configuration

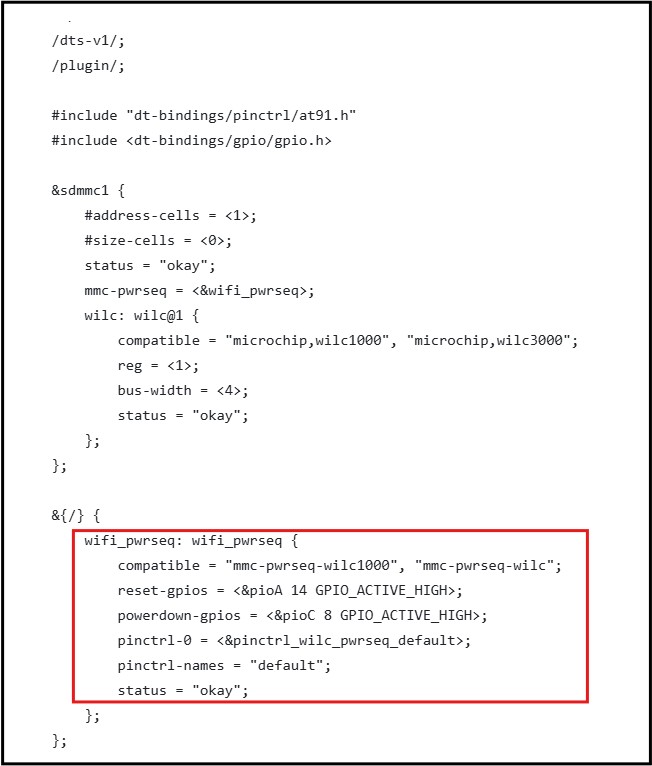

In the following example, the wifi_pwrseq node in the device tree is not configured with any clock.

We aim to configure this node to use a programmable clock, namely PCK0. To achieve the precise

frequency of 32.768 kHz (TD_CLK), the WILC driver must be switched to a generic one by

updating the compatible property from microchip,wilc1000 or

microchip,wilc to mmc-pwrseq-simple. The clock source is provided by

the Power Management Controller (PMC), with the clock type set to system and the

ID set to 8, which corresponds to programmable clock 0 (PCK0). By default, the parent of

this programmable clock is the Monitoring Domain Slow Clock (MD_SLCK), as described in

the SAM9X60 data sheet (see References).

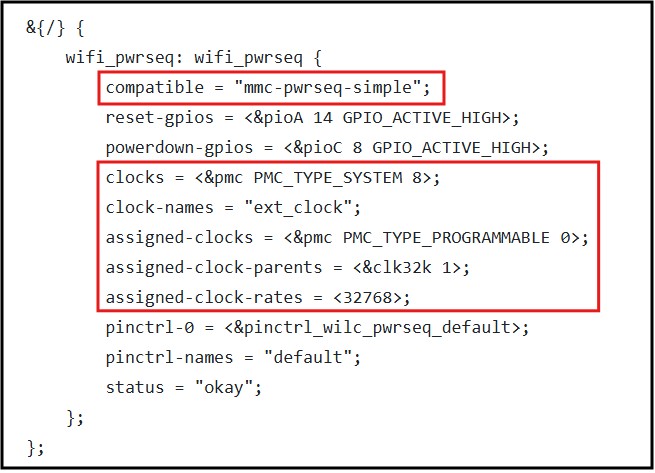

However, using the assigned-clock-parents property, we explicitly set the parent of PCK0 to the Timing Domain Slow Clock (TD_SLCK). The following device tree source snippet shows the changes required to achieve this configuration.