3 Status of the Synthesis Process

Understanding the synthesis status indicator

A synthesis process converts a logic design into bitstream form which can be loaded into the CLB. This is triggered by clicking the Synthesize button.

The outcome of the synthesis process is indicated by the status indicator and the resource view.

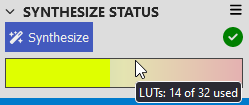

Successful Synthesis

A green indicator will show when the synthesis succeeds and the resource view is updated.

The resource view indicates how much of the CLBs resources have been used, and hovering the mouse over it gives additional information.

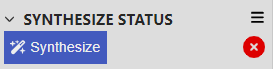

Failed Synthesis

A red indicator will show when synthesis has failed.

The nature of the failure can be determined by:

- Checking the problems/notifications panels for warnings about unconnected pins

- Downloading the ZIP and checking the backend log output. This must also be included when consulting Microchip support channels.

Resource Usage Debugging

- Try to use alternative outputs (eg: change IRQ0 to IRQ1)

- Try to remove some logic functionality

- Check that there are no unused modules included in the documents

- Check that there are no logic functions with pre-determined outputs (eg: a constant zero as an input to an AND gate)

When contacting Microchip support, include the ZIP file which was returned from the failing synthesis process.