16.3.3 IO1

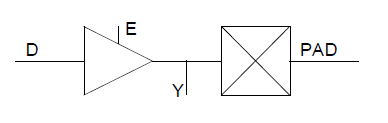

(Ask a Question)16.3.3.1 BIBUF

(Ask a Question)Bidirectional Buffer.

| Input | Output |

|---|---|

| D, E, PAD | PAD, Y |

| MODE | E | D | PAD | Y |

|---|---|---|---|---|

| OUTPUT | 1 | D | D | D |

| INPUT | 0 | X | Z | X |

| INPUT | 0 | X | PAD | PAD |

16.3.3.2 BIBUF_DIFF

(Ask a Question)Bidirectional Buffer, Differential I/O.

| Input | Output |

|---|---|

| D, E, PADP, PADN | PADP, PADN, Y |

| MODE | E | D | PADP | PADN | Y |

|---|---|---|---|---|---|

| OUTPUT | 1 | 0 | 0 | 1 | 0 |

| OUTPUT | 1 | 1 | 1 | 0 | 1 |

| INPUT | 0 | X | Z | Z | X |

| INPUT | 0 | X | 0 | 0 | X |

| INPUT | 0 | X | 1 | 1 | X |

| INPUT | 0 | X | 0 | 1 | 0 |

| INPUT | 0 | X | 1 | 0 | 1 |

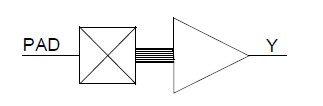

16.3.3.3 CLKBIBUF

(Ask a Question)Bidirectional Buffer with Input to global network.

| Input | Output |

|---|---|

| D, E, PAD | PAD, Y |

| D | E | PAD | Y |

|---|---|---|---|

| X | 0 | Z | X |

| X | 0 | 0 | 0 |

| X | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

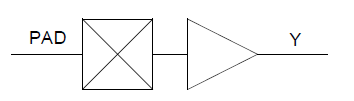

16.3.3.4 CLKBUF

(Ask a Question)Input Buffer to global network.

| Input | Output |

|---|---|

| PAD | Y |

| PAD | Y |

|---|---|

| 0 | 0 |

| 1 | 1 |

16.3.3.5 CLKBUF_DIFF

(Ask a Question)Differential I/O macro to global network, Differential I/O.

| Input | Output |

|---|---|

| PADP, PADN | Y |

| PADP | PADN | Y |

|---|---|---|

| Z | Z | Y |

| 0 | 0 | X |

| 1 | 1 | X |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

16.3.3.6 INBUF

(Ask a Question)Input Buffer.

| Input | Output |

|---|---|

| PAD | Y |

| PAD | Y |

|---|---|

| Z | X |

| 0 | 0 |

| 1 | 1 |

16.3.3.7 INBUF_DIFF

(Ask a Question)Input Buffer, Differential I/O.

| Input | Output |

|---|---|

| PADP, PADN | Y |

| PADP | PADN | Y |

|---|---|---|

| Z | Z | X |

| 0 | 0 | X |

| 1 | 1 | X |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

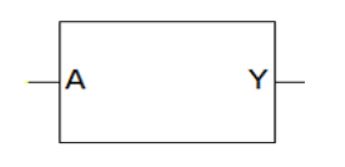

16.3.3.8 IOINFF_BYPASS

(Ask a Question)The I/O input bypass macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| A | Y |

| A | Y |

|---|---|

| 0 | 0 |

| 1 | 1 |

16.3.3.9 IOENFF_BYPASS

(Ask a Question)The I/O enable bypass macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| A | Y |

| A | Y |

|---|---|

| 0 | 0 |

| 1 | 1 |

16.3.3.10 IOOUTFF_BYPASS

(Ask a Question)The I/O output bypass macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| A | Y |

| A | Y |

|---|---|

| 0 | 0 |

| 1 | 1 |

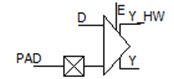

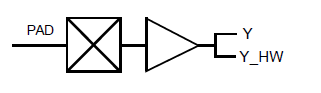

16.3.3.11 IOPAD_BI

(Ask a Question)The I/O output bypass macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| D, E, PAD | PAD, Y, Y_HW |

| MODE | E | D | PAD | Y | Y_HW |

|---|---|---|---|---|---|

| OUTPUT | 1 | D | D | D | D |

| INPUT | 0 | X | Z | X | X |

| INPUT | 0 | X | PAD | PAD | PAD |

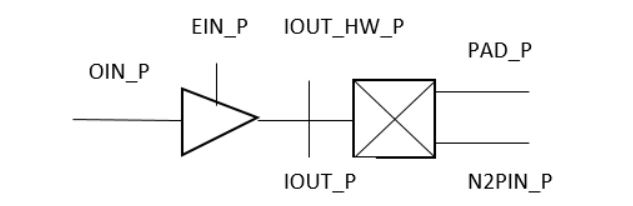

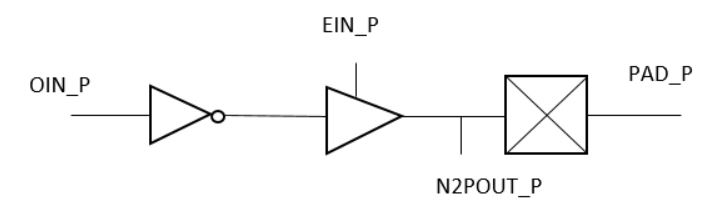

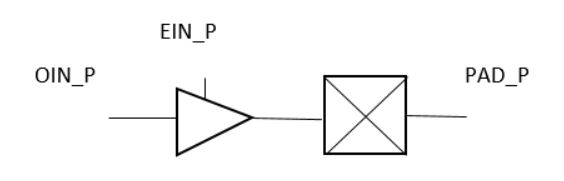

16.3.3.12 IOPADP_BI

(Ask a Question)The I/O PAD bi-directional macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| N2PIN_P, OIN_P, EIN_P, PAD_P | PAD_P, IOUT_P, IOUT_HW_P |

| MODE | EIN_P | OIN_P | PAD_P | N2PIN_P | IOUT_P | OUT_HW_P |

|---|---|---|---|---|---|---|

| OUTPUT | 1 | 0 | 0 | 1 | 0 | 0 |

| OUTPUT | 1 | 1 | 1 | 0 | 1 | 1 |

| INPUT | 0 | X | Z | Z | X | X |

| INPUT | 0 | X | 0 | 0 | X | X |

| INPUT | 0 | X | 1 | 1 | X | X |

| INPUT | 0 | X | 0 | 1 | 0 | 0 |

| INPUT | 0 | X | 1 | 0 | 1 | 1 |

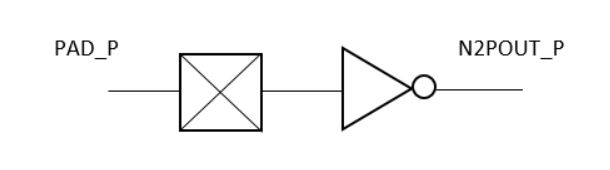

16.3.3.13 IOPADN_BI

(Ask a Question)The I/O PAD bi-directional macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| OIN_P, EIN_P, PAD_P | PAD_P, N2POUT_P |

| MODE | EIN_P | OIN_P | PAD_P | N2POUT_P |

|---|---|---|---|---|

| OUTPUT | 1 | 1 | 0 | 0 |

| OUTPUT | 1 | 0 | 1 | 1 |

| INPUT | 0 | X | Z | X |

| INPUT | 0 | X | 0 | X |

| INPUT | 0 | X | 1 | X |

| INPUT | 0 | X | 0 | 0 |

| INPUT | 0 | X | 1 | 1 |

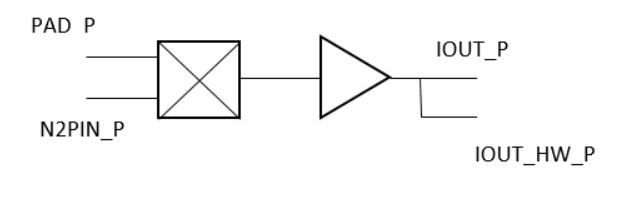

16.3.3.14 IOPADP_IN

(Ask a Question)The I/O PAD input macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| PAD_P, N2PIN_P | IOUT_P, IOUT_HW_P |

| PAD_P | N2PIN_P | IOUT_P | IOUT_HW_P |

|---|---|---|---|

| Z | X | X | X |

| 0 | X | 0 | 0 |

| 1 | X | 1 | 1 |

16.3.3.15 IOPADN_IN

(Ask a Question)The I/O PAD input macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| PAD_P | N2POUT_P |

| PAD_P | N2POUT_P |

|---|---|

| 0 | 1 |

| 1 | 0 |

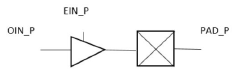

16.3.3.16 IOPADP_TRI

(Ask a Question)The I/O PAD tristate output macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| OIN_P, EIN_P | PAD_P |

| OIN_P | EIN_P | PAD_P |

|---|---|---|

| X | 0 | Z |

| OIN_P | 1 | OIN_P |

16.3.3.17 IOPADN_TRI

(Ask a Question)The I/O PAD tristate output macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| OIN_P, EIN_P | PAD_P |

| OIN_P | EIN_P | PAD_P |

|---|---|---|

| X | 0 | Z |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

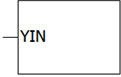

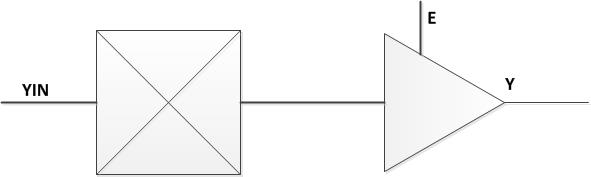

16.3.3.18 IO_DIFF

(Ask a Question)The I/O Differential macro is available only in post-layout netlist (place holder to reserve the N location).

Input = YIN

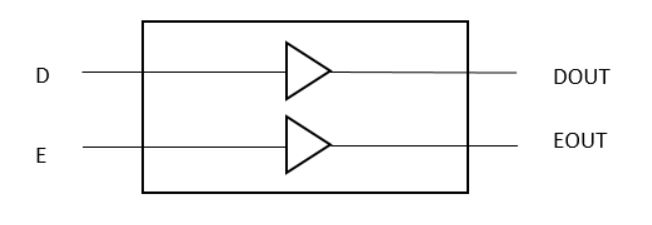

16.3.3.19 IOTRI_OB_EB

(Ask a Question)The I/O feed through macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| D, E | DOUT, EOUT |

| D | DOUT |

|---|---|

| 0 | 0 |

| 1 | 1 |

| E | EOUT |

|---|---|

| 0 | 0 |

| 1 | 1 |

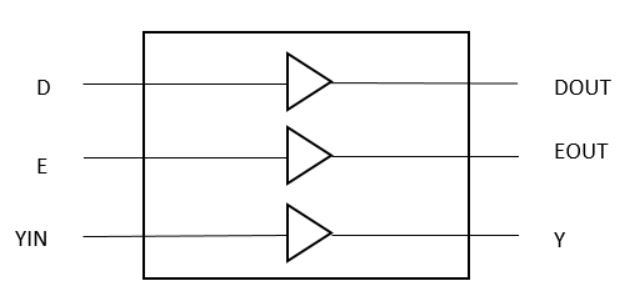

16.3.3.20 IOBI_IB_OB_EB

(Ask a Question)The I/O feed through macro is available in post-layout netlist only.

| Input | Output |

|---|---|

| D, E, YIN | DOUT, EOUT, Y |

| D | DOUT |

|---|---|

| 0 | 0 |

| 1 | 1 |

| E | EOUT |

|---|---|

| 0 | 0 |

| 1 | 1 |

| YIN | Y |

|---|---|

| 0 | 0 |

| 1 | 1 |

16.3.3.21 OUTBUF

(Ask a Question)Output buffer.

| Input | Output |

|---|---|

| D | PAD |

| D | PAD |

|---|---|

| 0 | 0 |

| 1 | 1 |

16.3.3.22 OUTBUF_DIFF

(Ask a Question)Output buffer, Differential I/O.

| Input | Output |

|---|---|

| D | PADP, PADN |

| D | PADP | PADN |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

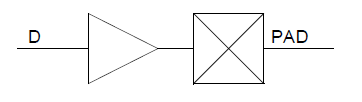

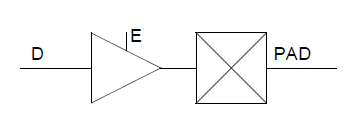

16.3.3.23 TRIBUFF

(Ask a Question)Tristate output buffer.

| Input | Output |

|---|---|

| D, E | PAD |

| D | E | PAD |

|---|---|---|

| X | 0 | Z |

| D | 1 | D |

16.3.3.24 TRIBUFF_DIFF

(Ask a Question)Tristate output buffer, Differential I/O.

| Input | Output |

|---|---|

| D, E | PADP, PADN |

| D | E | PADP | PADN |

|---|---|---|---|

| X | 0 | Z | Z |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

16.3.3.25 DDR_IN

(Ask a Question)The DDR_IN macro is available for both pre-layout and post-layout simulation flows. It consists of two SLE macros and a latch. The input D must be connected to an I/O.

| Input | Output | |

|---|---|---|

| Name | Function | Name |

| D | Data input | QR QF |

| CLK | Clock input | |

| EN | Active High CLK enable | |

| ALn | Asynchronous load. This active low signal either sets the register or clears the register depending on the value of ADn. | |

| ADn1 | Static asynchronous load data. When ALn is active, QR and QF go to the complement of ADn. | |

| SLn | Synchronous load. This active low signal either sets the register or clears the register depending on the value of SD, at the rising edge of CLK. | |

| SD1 | Static synchronous load data. When SLn is active (that is, low), QR and QF go to the value of SD at the rising edge of CLK. | |

- ADn and SD are static inputs defined at design time and need to be tied to 0 or 1.

| ALn | CLK | EN | SLn | dfn+1 (Internal Signal) | QRn+1 | QFn+1 |

|---|---|---|---|---|---|---|

| 0 | X | X | X | !ADn | !ADn | !ADn |

| 1 | Not rising | X | X | dfn | QRn | QFn |

| 1 | ↑ | 0 | X | dfn | QRn | QFn |

| 1 | ↑ | 1 | 0 | dfn | SD | SD |

| 1 | ↑ | 1 | 1 | dfn | D | dfn |

| 1 | ↓ | X | X | D | QRn | QFn |

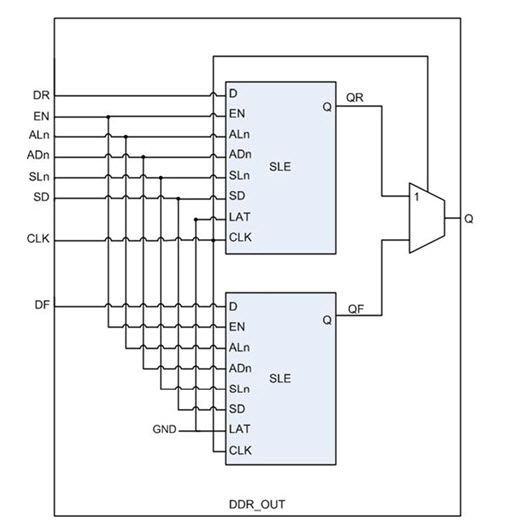

16.3.3.26 DDR_OUT

(Ask a Question)The DDR_OUT macro is an output DDR cell and is available for pre-layout simulation. It consists of two SLE macros. The output Q must be connected to an I/O.

| Input | Output | |

|---|---|---|

| Name | Function | |

| DR | Data input (Rising Edge) | Q |

| DF | Data input (Falling Edge) | |

| CLK | Clock input | |

| EN | Active High CLK enable | |

| ALn | Asynchronous load. This active low signal either sets the register or clears the register depending on the value of ADn. | |

| ADn1 | Static asynchronous load data. When ALn is active, Q goes to the complement of ADn. | |

| SLn | Synchronous load. This active low signal either sets the register or clears the register depending on the value of SD, at the rising edge of CLK. | |

| SD1 | Static synchronous load data. When SLn is active (that is, low), Q goes to the value of SD at the rising edge of CLK. | |

- ADn and SD are static inputs defined at design time and need to be tied to 0 or 1.

| ALn | CLK | EN | SLn | QRn+1 | QFn+1 | Qn+1 |

|---|---|---|---|---|---|---|

| 0 | X | X | X | !ADn | !ADn | !ADn |

| 1 | 1 | X | X | QRn | QFn | QRn |

| 1 | ↑ | 0 | X | QRn | QFn | QRn+1 |

| 1 | ↑ | 1 | 0 | SD | SD | QRn+1 |

| 1 | ↑ | 1 | 1 | DR | DF | QRn+1 |

| 1 | 0 | X | X | QRn | QFn | QFn |

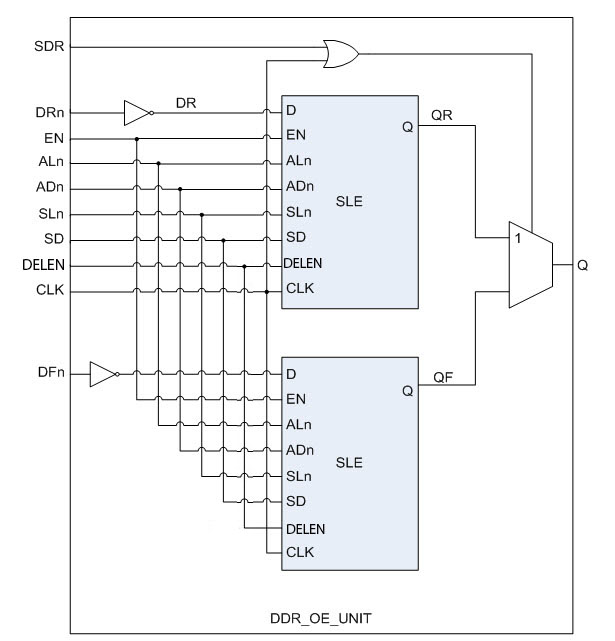

16.3.3.27 DDR_OE_UNIT

(Ask a Question)The DDR_OE_UNIT macro is an output DDR cell that is only available for post-layout simulations. Every DDR_OUT instance is replaced by DDR_OE_UNIT during compile. The DDR_OE_UNIT macro consists of a DDR_OUT macro with inverted data inputs and SDR control.

| Input | Output | |

|---|---|---|

| Name | Function | |

| DRn | Data input (Rising Edge) | Q |

| DFn | Data input (Falling Edge) | |

| CLK | Clock input | |

| EN | Active High CLK enable | |

| ALn | Asynchronous load. This active low signal either sets the register or clears the register depending on the value of ADn. | |

| ADn | Static asynchronous load data. When ALn is active, Q goes to the complement of ADn. | |

| SLn | Synchronous load. This active low signal either sets the register or clears the register depending on the value of SD, at the rising edge of CLK. | |

| SD | Static synchronous load data. When SLn is active (that is, low), Q goes to the value of SD at the rising edge of CLK. | |

| SDR | Controls whether the cell operates in DDR (SDR = 0) or SDR (SDR = 1) modes. | |

| SDR | ALn | CLK | EN | SLn | QRn+1 | QFn+1 | Qn+1 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | X | X | X | !ADn | !ADn | !ADn |

| 0 | 1 | 1 | X | X | QRn | QFn | QRn |

| 0 | 1 | ↑ | 0 | X | QRn | QFn | QRn+1 |

| 0 | 1 | ↑ | 1 | 0 | SD | SD | QRn+1 |

| 0 | 1 | ↑ | 1 | 1 | !DRn | !DFn | QRn+1 |

| 0 | 1 | 0 | X | X | QRn | QFn | QFn |

16.3.3.28 IOIN_IB

(Ask a Question)Buffer macro available in post-layout netlist only.

| Input | Output |

|---|---|

| YIN, E | Y |

| YIN | Y |

|---|---|

| Z | X |

| 0 | 0 |

| 1 | 1 |

16.3.3.29 IOPAD_IN

(Ask a Question)Input I/O macro available in post-layout netlist only.

| Input | Output |

|---|---|

| PAD | Y, Y_HW |

| PAD | Y, Y_HW |

|---|---|

| Z | X |

| 0 | 0 |

| 1 | 1 |

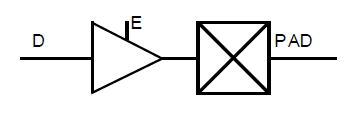

16.3.3.30 IOPAD_TRI

(Ask a Question)Tri-state output buffer available in post-layout netlist only.

| Input | Output | |

|---|---|---|

| D, E | PAD | |

| D | E | PAD |

|---|---|---|

| X | 0 | Z |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

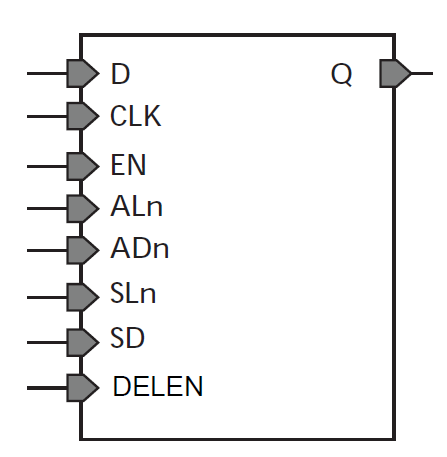

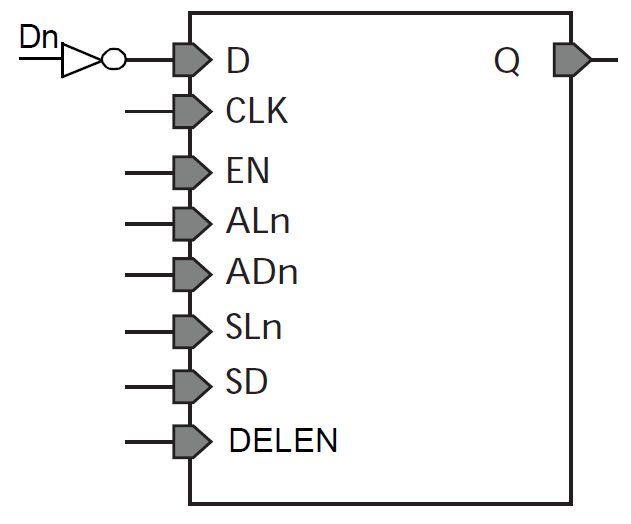

16.3.3.31 IOINFF

(Ask a Question)Registered input I/O macro available only in post-layout netlist.

| Input | Output | |

|---|---|---|

| Name | Function | Q |

| D | Data | |

| CLK | Clock | |

| EN | Enable | |

| ALn | Asynchronous Load (Active-Low) | |

| ADn1 | Asynchronous Data (Active-Low) | |

| SLn | Synchronous Load (Active-Low) | |

| SD1 | Synchronous Data | |

| DELEN1 | Enable Single-event Transient mitigation | |

- ADn, SD, and DELEN are static signals defined at design time and need to be tied to 0 or 1.

| ALn | ADn | CLK | EN | SLn | SD | D | Qn+1 |

|---|---|---|---|---|---|---|---|

| 0 | ADn | X | X | X | X | X | !ADn |

| 1 | X | Not rising | X | X | X | X | Qn |

| 1 | X | ↑ | 0 | X | X | X | Qn |

| 1 | X | ↑ | 1 | 0 | SD | X | SD |

| 1 | X | ↑ | 1 | 1 | X | D | D |

16.3.3.32 IOOEFF

(Ask a Question)Registered output I/O macro available only in post-layout netlist. The IOOEFF is an SLE_RT with an inverted data input.

| Input | Output | |

|---|---|---|

| Name | Function | Q |

| D | Data | |

| CLK | Clock | |

| EN | Enable | |

| ALn | Asynchronous Load (Active Low) | |

| ADn1 | Asynchronous Data (Active Low) | |

| SLn | Synchronous Load (Active Low) | |

| SD1 | Synchronous Data | |

| DELEN1 | Enable Single-event Transient mitigation | |

- ADn, SD, and DELEN are static signals defined at design time and need to be tied to 0 or 1.

| ALn | ADn | CLK | EN | SLn | SD | D | Qn+1 |

|---|---|---|---|---|---|---|---|

| 0 | ADn | X | X | X | X | X | !ADn |

| 1 | X | Not rising | X | X | X | X | Qn |

| 1 | X | ↑ | 0 | X | X | X | Qn |

| 1 | X | ↑ | 1 | 0 | SD | X | SD |

| 1 | X | ↑ | 1 | 1 | X | D | !D |