3.5.3.1 Circuit Topology

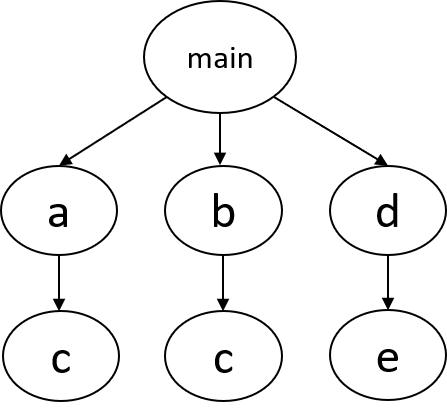

(Ask a Question)Each C/C++ function corresponds to a hardware module in Verilog. For instance, if we have a software program with the following call graph:

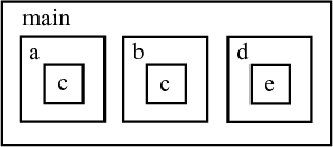

main calls a, b, and d, each of which calls c, c, and e, respectively. Notice that function c is called by both a and b. One way to create this system in hardware is to instantiate one module within another module, in a nested hierarchy, following how the functions are called in software:

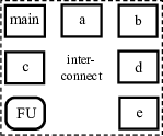

This architecture is employed by some of the other HLS tools, but it can create an unnecessary replication of hardware. Notice how module c has to be created twice, since the function c is called from different parent functions. In SmartHLS™, we instantiate all modules at the same level of hierarchy, and automatically create the necessary interconnect to connect them together.

This prevents modules from being unnecessarily replicated, saving area. The hardware system may also use a functional unit (denoted as FU in the figure), such as a floating-point unit, which is also created at the same level. This architecture also allows such units, which typically consume a lot of area, to be shared between different modules.

For a small function, or for a function that is only called once in software, SmartHLS may decide to inline the function into its parent function to improve performance. Any inlined function is included as part of its parent function, so there will not be a separate module in the Verilog for the inlined function. Thus you may not find all the software functions in the generated hardware.