4 Implementing a Simple Clock Follower in the LAN8650/1

Figure 4-1 shows a block diagram for a synchronized mixing segment based on the LAN8650/1. The clock source could be a simple node that sets the standard for the network but does not support the full IEEE 802.1AS standard. In this case, it must be able to generate and send Sync and Follow_up messages with correct timestamps to the shared medium. It could also be a more powerful node that connects to an external grandmaster via a point-to-point network that is not shown. Such a node will supports the full IEEE 802.1AS standard, although it may need modification to its protocol stacks so that it sends only supported traffic onto the mixing segment.

The clock followers are processors that do not contain MACs and so will use SPI to connect to the LAN8650/1. They will use the wall clock and packet timestamping features to synchronize clocks using only received Sync and Follow_up messages. The quality of the clock can be monitored using the 1PPS output function. The event generator can be used to provide events synchronized to the wall clock and event timestamping can be used to timestamp external events.

Software Configuration for a Clock Follower

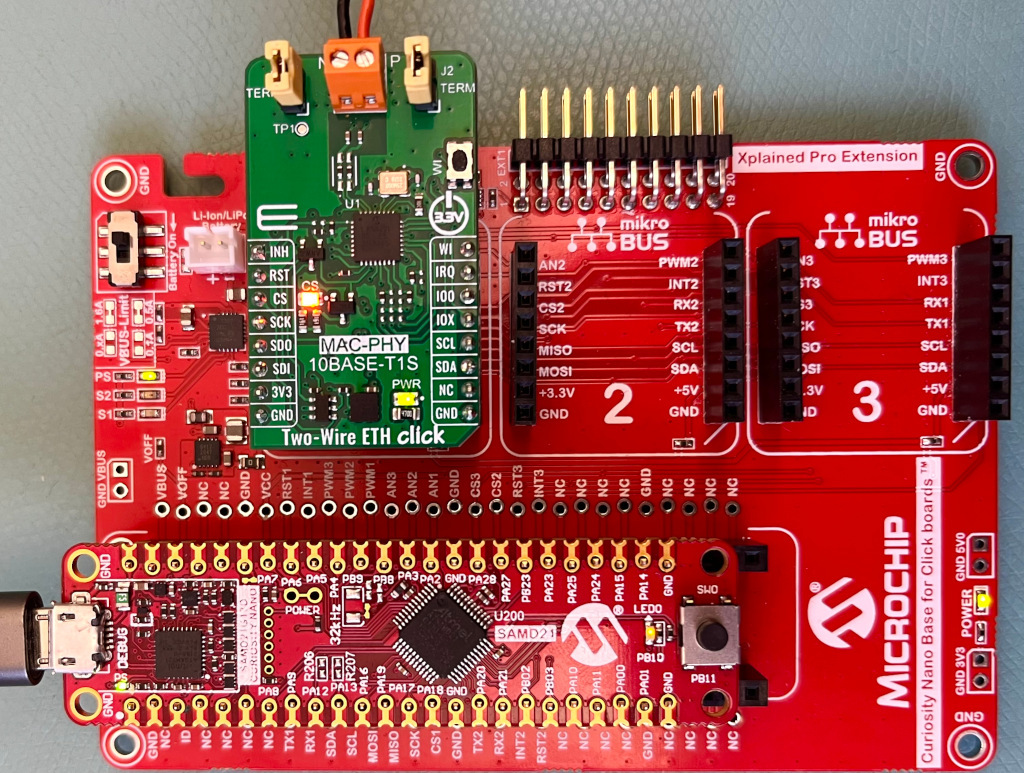

Any processor using a LAN8650/1 requires a driver to interface to the device, such as the LAN865x Driver included in MPLAB® Harmony v3. This driver will process both inbound and outbound Ethernet packets as well as control and monitor the device.

- Configure the pattern matcher so that timestamps are generated following the Start-of-Frame delimiter on all receive packets

- Set the receive match mask to 0xFFFFFF by writing to the Receive Match Mask (High) (RXMMSKH) and Receive Match Mask (Low) (RXMMSHL) registers

- Set the Receive Match Location (RXMLOC) to 0

- Configure the wall clock increment register to

the nominal value of 40 ns for each tick of the 25 MHz oscillator

- Set the TSU_Timer Increment Register (MAC_TI) to 0x28

- Set the FTSE bit in the OA_CONFIG0 register to enable timestamping.

- Set the FTSS bit in the OA_CONFIG0 register to '1' for 64-bit timestamps or '0' for 32-bit timestamps

PTP Message Handling

- The Sync message contains a sequence number. This sequence number is repeated in the Follow-up packet. These numbers should be checked to ensure the timestamp corresponds to the correct Sync message.

- The timestamp tSYNCTX is found directly inside the Follow_up packet. In the example, the TC6 driver delivers the full Ethernet packet and the example software extracts it.

- The timestamp tSYNCRX is captured by the packet timestamp unit and is provided to the controller as described in the SPI MAC-PHY protocol. The LAN865x Driver copies timestamps for all PTP packets and passes them as arguments to the handlePtp function.

Sync packets are typically sent at 8 or 16 packets per second. In many systems, the clocks are fully synchronized after less than 20 Sync messages

Synchronizing the Clock

After processing the PTP messages, the timestamps are used by the clock synchronization algorithm. This algorithm implements a software phase‑locked loop that controls the local wall clock, such as one shown in Figure 4-2. The algorithm will process the input timestamps and determine the difference between the source wall clock and the local wall clock, which is the time error (sometimes called phase error). Most algorithms also track the time between Sync timestamps on both source and follower and use the resulting rate ratio to track frequency drift. Synchronization algorithms can vary from simple filters for networks that have low traffic loads and therefore minimal jitter to algorithms containing PI or PID controllers for noisier networks.

This method requires an estimate of the propagation delay between the clock follower and each node. This can be done by measurement or simulation of the mixing segment. Note that if the propagation delay is small, that is, if the mixing segment is short, then the clock servo algorithm may choose to omit the propagation delay. As a rule of thumb, a propagation delay corresponding to one meter of twisted pair cable is approximately 5 ns.

- Initialization: At start-up, or if the input clock source changes, the clocks will vary greatly. In this phase, the clock servo algorithm will normally directly write the values of the wall clock. This is done by writing to the registers TSU Timer Seconds High Register (MAC_TSH), TSU Timer Seconds Low Register (MAC_TSL) and TSU Timer Nanoseconds Register (MAC_TSN) . This is normally done once, then the algorithm will move to the Unlocked state.

- Unlocked: After initialization, the clock needs further alignment before it is ready to be used. This state can also occur when a previously locked clock is now experiencing enough jitter that it causes errors that cannot be handled in the locked states. In this state, the algorithm will use large adjustments of the wall clock by writing to the Timer Adjust (MAC_TA) register. When the clock error is withing limits, the stage will change to Locked (Coarse).

- Locked (Coarse): In this state, the clock error is small enough so that the clock frequencies are very closely synchronized, but the phase error is still large. Depending on the algorithm, adjustments on the order of a few nanoseconds may be made via the MAC_TA register, or adjustments may be limited to modifying the increment with changes to the MAC_TI and MAC_TISUBNS registers.

- Locked (Fine). This state is reached when the clock error is within acceptable limits, the frequencies are well matched and wall clock has only a small phase error, which can be corrected with either small changes to the increment registers or time adjust register. The error limit as well as the correction method are dependent on the total noise and jitter of the system, including the Grandmaster clock.

The quality of synchronization can be examined by comparing a 1PPS output from the clock follower to that of the clock source. In the example, the 1PPS output is enabled the first time that the software enters the FINE state.

Results

An example of the code for both a PTP Grandmaster and PTP follower can be found online under github.com/MicrochipTech/LAN865x-TimeSync.

The Grandmaster device includes features such as the ability to delay the SYNC and FOLLOWUP messages by a predetermined, variable amount for robustness testing of the PTP follower and the ability to transmit iPerf messages between SYNC messages. The Grandmaster device follows the correct method for accessing registers on the LAN8650/1 for transmitting a timestamp.

The PTP follower device contains only simple algorithms to synchronize its internal clock. Before synchronizing the time, the PTP follower uses the first few SYNC and FOLLOWUP messages to guess the difference between its own clock frequency and the clock frequency of the Grandmaster. It adjusts this once before beginning the clock synchronization algorithm. During this algorithm, the follower only uses simple FIR filters to adjust its own internal time. This makes the algorithm extremely simple and able to be used in nearly any microcontroller. The different states described above are reached when the time difference between the internal times reach various thresholds. Time adjustments are done exclusively through the time adjust register, MAC_TA.

Comparing the 1PPS output of this node to the clock source shows the follower clock to have a maximum time difference of 100 ns, with an 8 ns mean and standard deviation of 25 ns. This performance is acceptable for many applications. If more precision is required, or the end system has more jitter, the references section contains additional information for more complex clock synchronization algorithms.