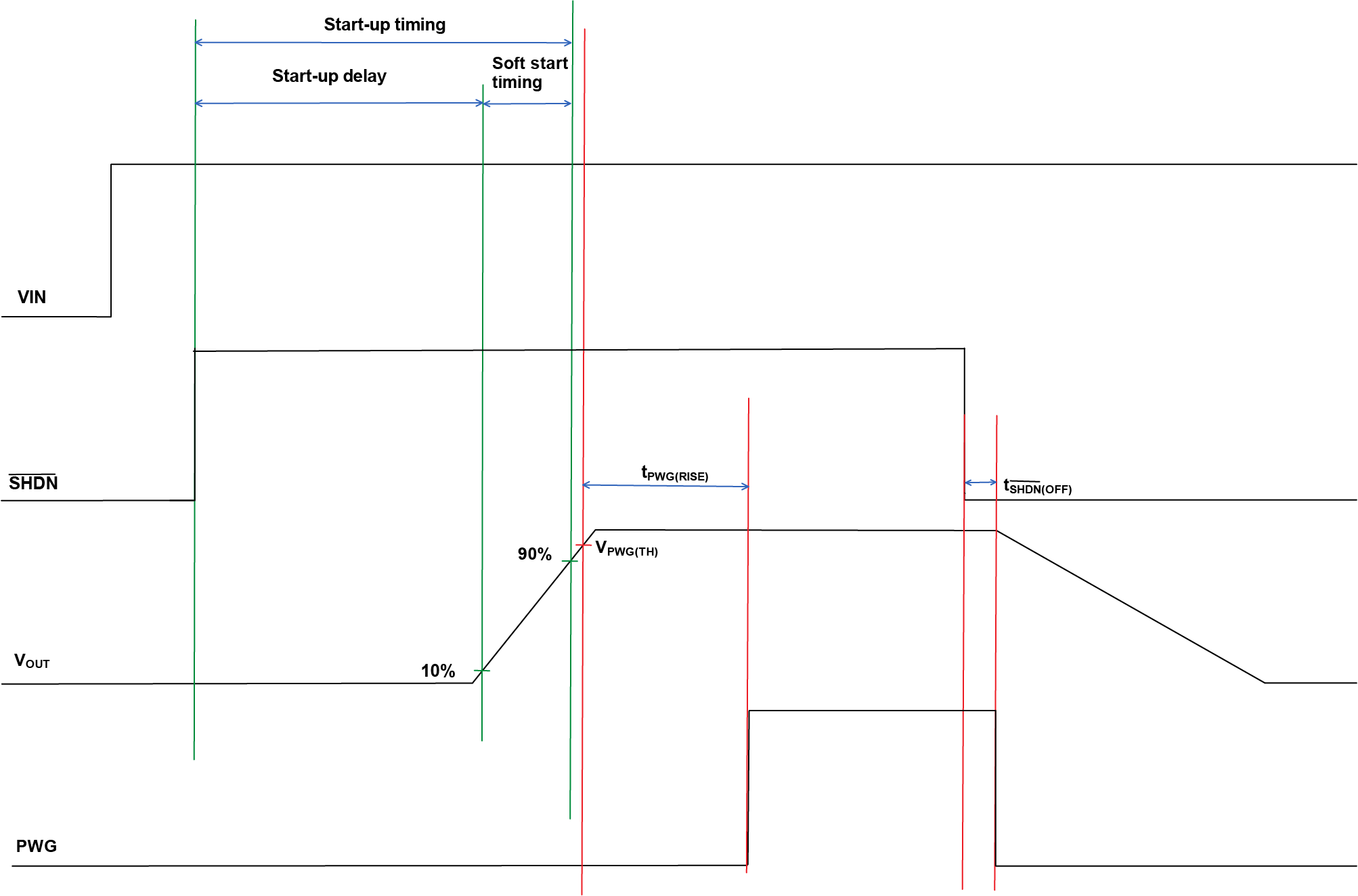

2.7 Power Good

The Power Good function is a low voltage open drain output which can be used to monitor the output of the LDO in relation to the Power Good Threshold level (VPWG(TH)), which is typically 94% of the output voltage.

During a normal start up sequence the open drain output is held low until the monitored regulated output voltage reaches the value of VPWG(TH). After which the power good time delay (tPWG(RISE)) will start, and after 98 µs typically the PWG pin will become inactive and can be pulled high by the external pull up resistor connected to VOUT or a separate supply rail that is below 5.5V.

During transient events, false triggering of the Power Good signal is prevented by means of time delay (tPWG(FALL)), typically, of 105 µs. After the internal circuitry detects the regulated output falling below the VPWG(TH)minus VPWG(HYS), the open drain output won’t be pulled low until the time delay passes. When the SHDN is pulled low, if the requirements for a valid signal are met, then the Power Good open drain will be pulled low. The output will be discharged by the output discharge block by means of 105Ω resistor pulled down to GND.