7 I/O States During Programming

(Ask a Question)The following table lists the I/O states that apply during various stages of programming.

| I/O Type | I/O States | ||

|---|---|---|---|

| JTAG Programming | SPI Slave Programming | SPI Master Programming (IAP/Auto Update) | |

| System controller I/O | Enabled. | Enabled. | Enabled. |

| XCVR reference clock inputs | Not affected. | Not affected. | Not affected. May be kept alive during IAP using loopback mode, allowing the XCVR link to be kept active. |

| XCVR data I/O | As set by the boundary scan cell. | Not affected. | Not affected. May be kept alive during IAP using loopback mode, allowing the XCVR link to be kept active. |

| GPIO and HSIO | I/Os are enabled, but the I/O state can be set using the boundary scan cell. | Can be weakly pulled up using the SPI slave instruction ISC_ENABLE. | Outputs are tristated and weakly pulled up. |

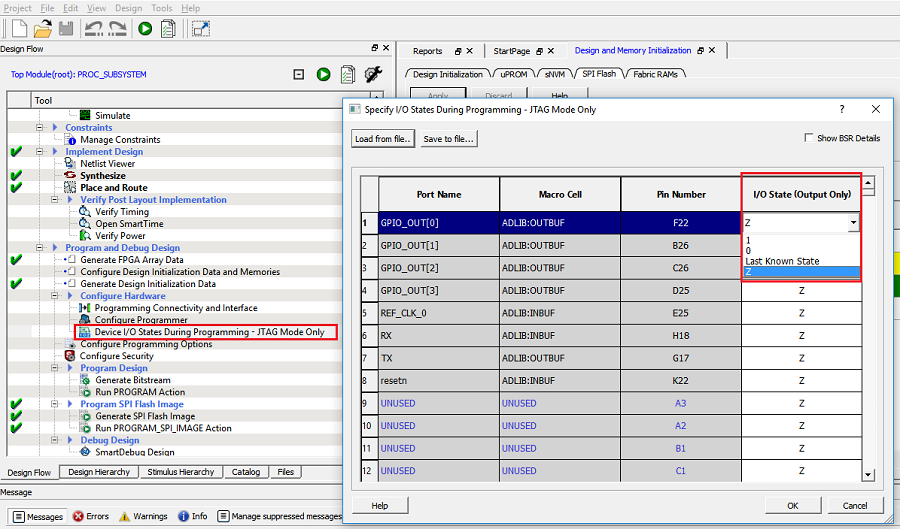

In Libero SoC, the I/O states can be set before JTAG programming, and these I/O states are held at the set values during JTAG programming. The following are the I/O output state settings:

- 1: I/O is set to drive out logic HIGH

- 0: I/O is set to drive out logic LOW

- Last Known State: I/O is set to the last value that was driven out before entering the programming mode and then held at that value during programming

- Z: I/O is tri-stated

The I/O output states can be set, as shown in the following figure.