4.2 Clocks

SAM9x5 and SAM9X60 support different crystals and manage PLLs differently. SAM9X60 provides generic clocks for most peripherals. Power Management Controller interfaces differ also, so software modifications are required.

| SAM9x5 | SAM9X60 |

|---|---|

| Clock Settings | |

| 32 KHz RC can be stopped 12 to 16 MHz crystal | 32 KHz RC always on 12 to 48 MHz crystal Note: The

engineering sample ROM code has crystal detection limitations, so only a

24 MHz crystal must be used if a Non-Volatile Memory (NVM) is programmed via

USB. |

Use the internal 32 kHz RC oscillator to

clock safely peripherals that do not need accuracy:

Only the RTC is connected to the external 32 KHz oscillator. | |

| Clock Setting Registers | |

|

CKGR_MOR sets the main oscillator. PMC_MCKR sets CPU and MCK clocks. |

CKGR_MOR includes additional bits:

|

| PLL Settings | |

|

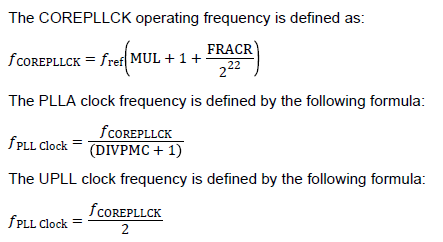

400 to 800 MHz PLLs PLLs are not fractional. PLLA clock ouput is: PLLACK = MAINCK / DIVA * MULA UPLL requires a 12 MHz crystal to generate 12x40 = 480 MHz frequency. |

600 to 1200 MHz PLLs PLLs are fractional. 12 MHz is not required to ensure USB clock accuracy.  Spread spectrum is embedded. |

| PLL Setting Registers | |

|

CKGR_PLLAR and PMC_PLLICPR set PLLA. PMC_USB sets USB clock. |

PMC_PLL_CTRL0, PMC_PLL_CTRL1 and PMC_PLL_ACR configure PLLs. PMC_PLL_SSR sets the spread spectrum. PMC_PLL_UPDT applies the modification in a glitch-free manner to the selected PLLs. ID = 0 for system PLL (former PLLA) ID = 1 for USB PLL PMC_USB sets USB clock. |

| Peripheral Clock Settings | |

|

PMC_PCR enables and disables a peripheral using its identifier (PID). Alternatively, PMC_PCER and PMC_PCDR can be used to enable and disable a peripheral using the PID. The peripheral clock status is shown in PMC_PCSR. |

Only PMC_PCR can be used. The peripheral clock status is shown in PMC_PCR, or alternatively in PMC_CSRx. |

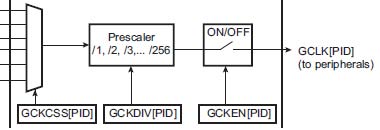

| Generic Clock Settings | |

| No generic clock is available. | A generic clock is available for most

(serial) peripherals, making it possible to use:

Source, divider and enable are selectable in PMC_PCR.  The generic clock status is shown in PMC_PCR, alternatively in PMC_GCSRx. Peripherals supporting the generic clocks are listed in the datasheet, in table Peripherals Identifiers. |

| Programmable Clock Settings | |

|

PMC_SCER and PMC_SCDR enable/disable PCKs. |

Bitfield size is different. PMC_SCER and PMC_SCDR enable/disable PCKs. |