1.6.2 Run-time Enabling of the Watchdog Timer

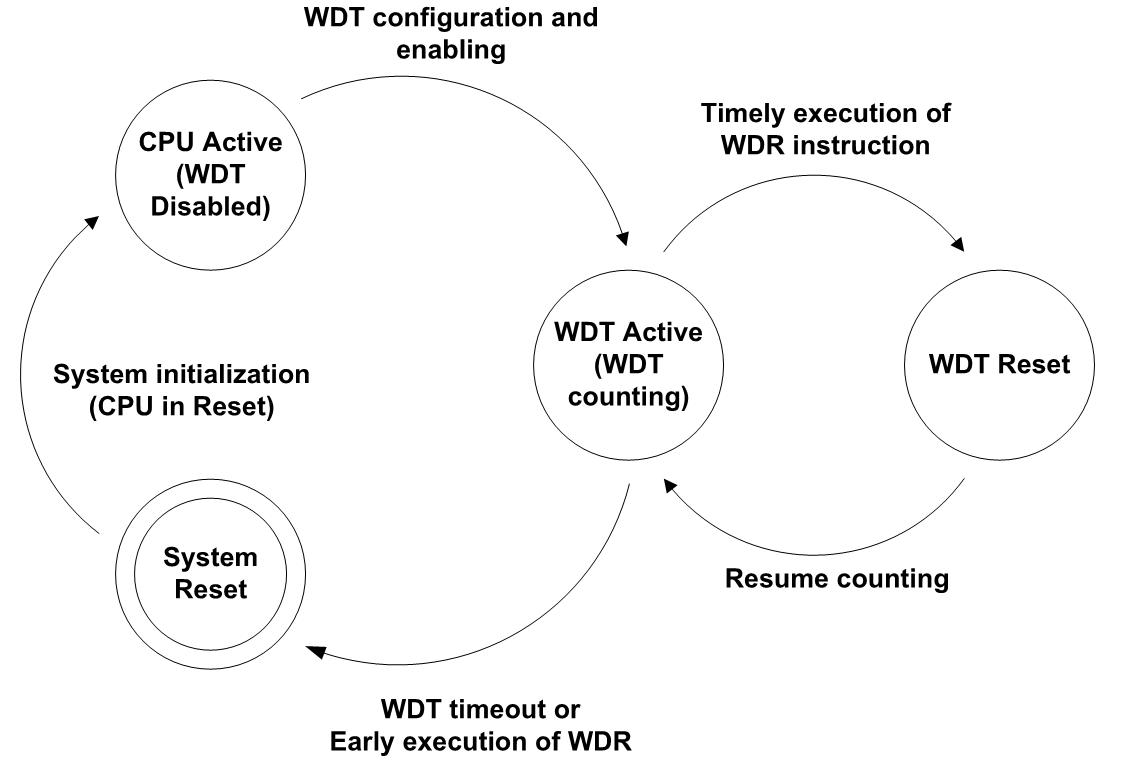

In some applications it can be required to disable the WDT to reduce the power consumption to an absolute minimum in Sleep mode. This can be the case in long life battery powered applications. If it is desirable to use the WDT in periods where the CPU is active, but not in Sleep modes, it is convenient to enable and disable the WDT, though this may reduce the protection offered by the WD.

To enable the WDT in run mode or to change the timeout period, a timed sequence must be used: The timed sequence involves the Configuration Change Protection register (CCP), which controls access to certain registers. After writing the signature 0xD8 to the CCP, the WDT can be reconfigured within the next four instruction cycles. During these four instruction cycles the global interrupts are automatically disabled to ensure that the timed sequence is not invalidated by an interrupt.

Within four instruction cycles after writing the 0xD8 signature to the CCP, the WDT control registers (CTRL and WINCTRL) can be modified. The procedure for doing so is specified in the data sheet, and examples on how to do it can be found in the code example for this application note.