5.1 MSS Clocks

(Ask a Question)The DDR PLL is dedicated to MSS DDR operation, generating the necessary clocks required for the DDR controller and DDR PHY. The DDR memory clock frequency must be less than or equal to 666.66 MHz for DDR3 and 800 MHz for DDR4. The SGMII PLL is dedicated to SGMII operation, generating the necessary clocks required for an off-chip SGMII PHY.

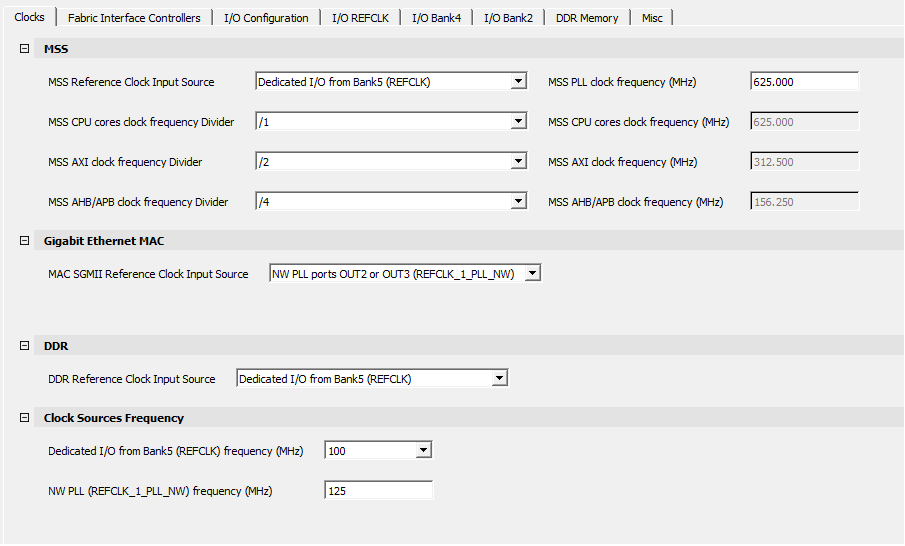

The MPLL takes the input from one of two sources (REFCLK I/O or PLL_NW outputs) and generates a master input clock (clk_in_mss). The clk_in_mss clock is used to generate the MSS clocks as listed in the following table.

| Clock Name | Description | Maximum Operating Frequency | Possible MPLL Output Division Ratios |

|---|---|---|---|

| CPU core clock (clk_cpu) | Clocks all the user processor cores | 625 MHz | 1, 2, 4, or 8 |

| MSS AXI clock (clk_axi) | Clocks MSS AXI buses and peripherals | 312.5 MHz | 1, 2, 4, or 8 |

| MSS AHB and APB clock (clk_ahb) | Clocks MSS AHB and APB buses and peripherals | 156.25 MHz | 2, 4, or 8 |

All the clocks shown in the preceding table are synchronous to each other and divided from the MPLL output with appropriate division values such that:

- CPU core clock must be greater than or equal to MSS AXI clock

- MSS AXI clock must be greater than or equal to MSS AHB and APB clock

The MPLL also generates the following clocks listed in the table.

| Clock Name | Description | Maximum Operating Frequency | Notes |

|---|---|---|---|

| Crypto clock (clk_in_crypto) | Clocks User Cryptoprocessor in MSS mode | 200 MHz | Configurable between 1 and 200 MHz |

| CAN clock (clk_in_clk) | Clocks MSS CAN controllers | 80 MHz | Must be a multiple of 8 MHz |

| eMMC/SD/SDIO clock (clk_in_emmc) | Clocks MSS eMMC/SD/SDIO controller | 200 MHz | Not configurable |

At power-on and after MSS reset, the MSS is clocked from the on-chip 80 MHz RC oscillator with CPU/AXI dividers set to 1 and the AHB/APB dividers set to 2. Embedded software, running on the E51 processor core, switches the MSS clock source dynamically to the user configuration.

The MSS Configurator provides a single place where all clocks related to the MSS can be configured. For more information, see PolarFire SoC Standalone MSS Configurator User Guide.