20.2.2.3.9 DDR Memory Partition

(Ask a Question)The DDR Memory Partition tab allows the DDR memory to be allocated to cached and non-cached regions depending on the amount of DDR memory physically connected.

In the DDR Memory Partition:

- The Offset Address (Base Address) for both cached and non-cached regions is fixed.

- High Address is the End Address based on the size.

- Users are expected to enter the Range.

Based on the Range selection, High Address and Physical DDR Offset is updated.

- When Range is set to zero, memory is not allocated in DDR.

- When Range is set to a nonzero value, it must be a multiple of 16 MB.

- Physical DDR Offset is allocation of DDR

memory (connected to the FPGA system) based on the nonzero Range value.Important: When Setup Physical DDR Address manually option is enabled, the default Physical DDR Offset Address is set as 0x0000_0000 for all the regions and it is up to the user to change this address (when the size of the allocated memory region is greater than 0 bytes). When the size of allocated memory region is zero bytes, the offset and high address are reported as N/A and remains as a read-only field.

- Range is allocated sequentially starting

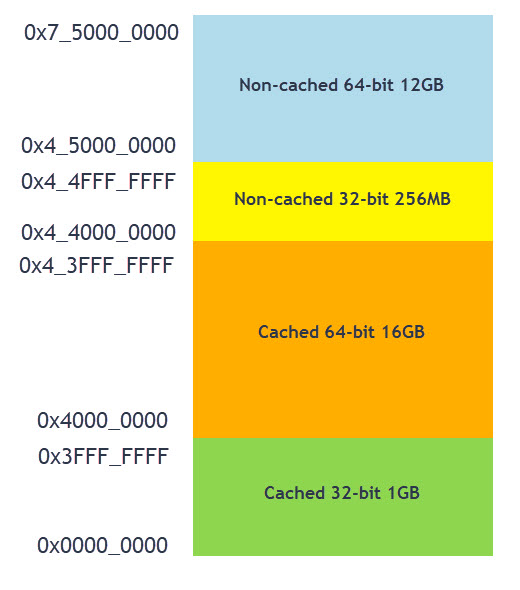

with 0x0000_0000 in the following order:

- Cached 32-bit

- Cached 64-bit

- Non-Cached 32-bit

- Non-Cached 64-bit

The following figure shows the graphical representation of how the Physical DDR Offset allocation is done based on the preceding ranges:

Figure 20-45. Physical DDR Offset — Graphical Representation