PECL, LVPECL

LVPECL and PECL are both offshoots of the older ECL technology, first introduced in the 1960s. PECL stands for Positive Emitter Coupled Logic as it operates off a positive voltage such as 5V, 3.3V, or 2.5V. PECL logic outputs are commonly used in high-speed clock distribution circuits. As a differential transmission scheme, PECL has the advantage of high noise immunity and the ability to drive high data rates over long line lengths. Another advantage of PECL includes good jitter performance due to the large voltage swing. Disadvantages include large power consumption (compared to a single-ended supply) due to the need for a 5V supply and external DC biasing.

Low Voltage PECL (LVPECL) refers to PECL circuits designed for use with 3.3V or 2.5V supply, the same supply voltages as for low voltage CMOS devices. LVPECL forms the basis of a number of protocols including Gigabit Ethernet and Fibre Channel. The LVPECL electrical specification is similar to Low Voltage Differential Signaling (LVDS), but operates with a larger differential voltage swing. LVPECL tends to be a little less power efficient than LVDS due to its ECL origins and larger swings. However, it can also operate at frequencies up to 10Gbps because of its ECL characteristics.

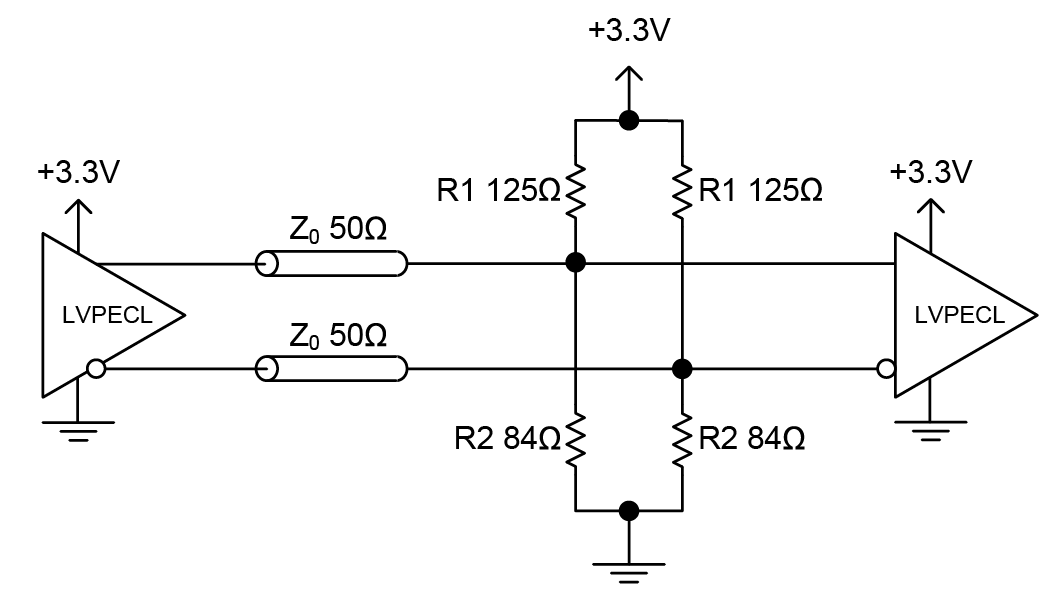

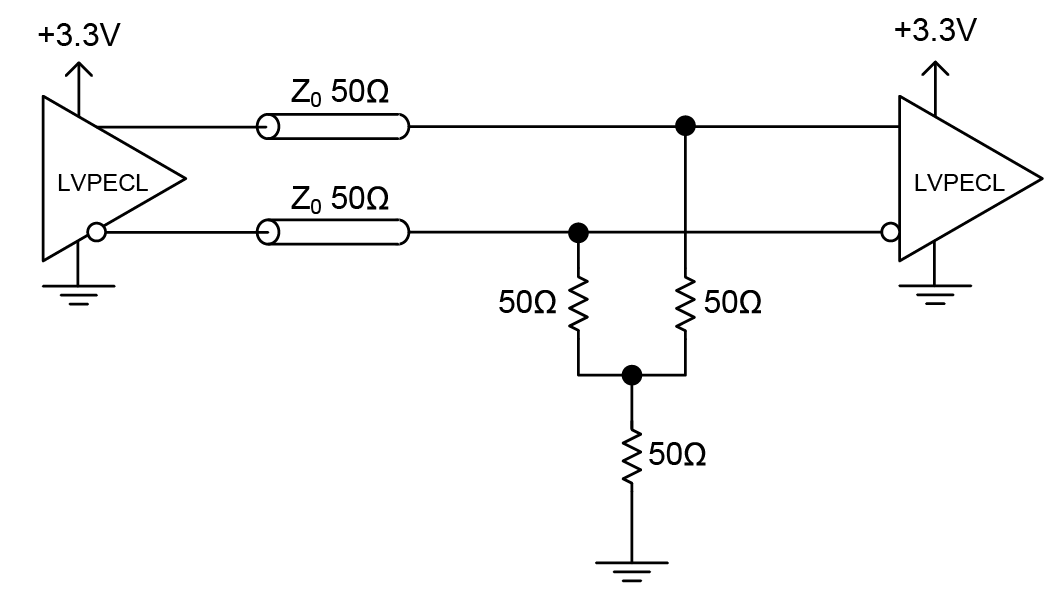

LVPECL output currents are typically 15mA and derived from an open emitter or FET source-drain outputs. This requires termination into a resistive load to produce a voltage. The intent for LVPECL is to use a 50Ω impedance trace and 50Ω thevenin equivalent load. This is usually implemented using Figure and an alternative scheme is shown in Figure . For best performance, the outputs should be equally terminated using the same method; an unused output should never be left floating. Also, differential receivers from different manufacturers can have different input tolerances (while still clustered around a common standard). Doing some homework on the requirements of the receiver can also help to optimize the transmission of the signal you are looking to terminate.