37.3.4 Acknowledge Sequence

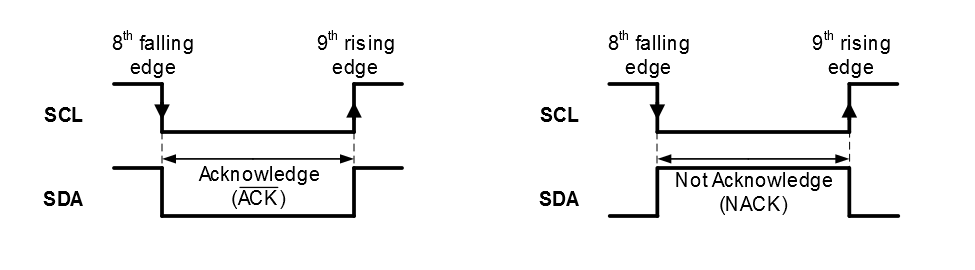

The 9th SCL pulse for any transferred address/data byte is reserved for the Acknowledge (ACK) sequence. During an Acknowledge sequence, the transmitting device relinquishes control of the SDA line to the receiving device. At this time, the receiving device must decide whether to pull the SDA line low (ACK) or allow the line to float high (NACK). Since the Acknowledge sequence is an active-low signal, pulling the SDA line low informs the transmitter that the receiver has successfully received the transmitted data.

0). When a client device receives a

matching address, or a receiver receives valid data, the ACKDT bit is cleared by user

software to indicate an ACK. If the client does not receive a

matching address, user software sets the ACKDT bit, indicating a NACK. In Client or

Multi-Host modes, if the Address Interrupt and Hold Enable (ADRIE) or Write Interrupt and Hold Enable (WRIE) bits are set, the clock is stretched after receiving a matching address or after the

8th falling edge of SCL when a data byte is received. This allows user software time to

determine the ACK/NACK response to send back to the

transmitter.0). When

the I2CxCNT register reaches a zero value, the ACKCNT bit can be cleared (ACKCNT =

0), indicating an ACK, or ACKCNT can be

set (ACKCNT = 1), indicating a NACK. The Acknowledge Time Status (ACKT) bit indicates whether or not the bus is in an Acknowledge sequence. The ACKT bit is set during an ACK/NACK sequence on the 8th falling edge of SCL and is cleared on the 9th rising edge of SCL, indicating that the bus is not in an ACK/NACK sequence.

Certain conditions will cause a NACK sequence to be sent automatically. A NACK sequence is generated by module hardware when any of the following bits are set:

- Transmit Write Error Status (TXWE)

- Transmit Underflow Status (TXU)

- Receive Read Error Status (RXRE)

- Receive Overflow Status (RXO)

The following figure shows ACK and NACK sequences.