4 3-to-8 Binary Decoder

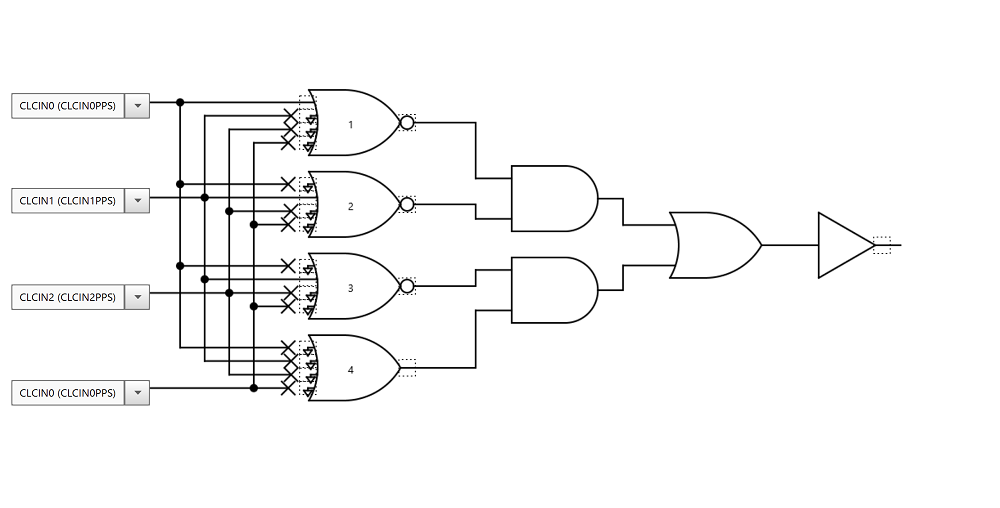

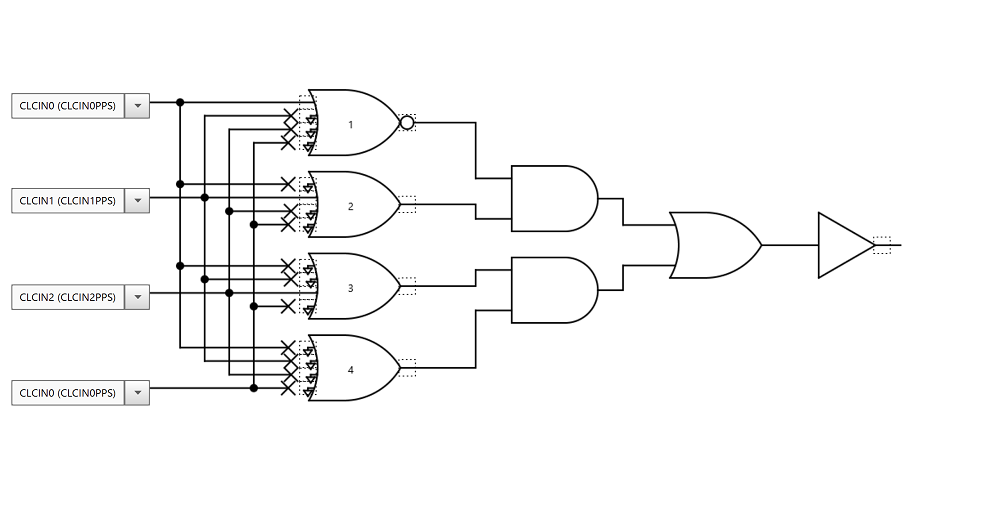

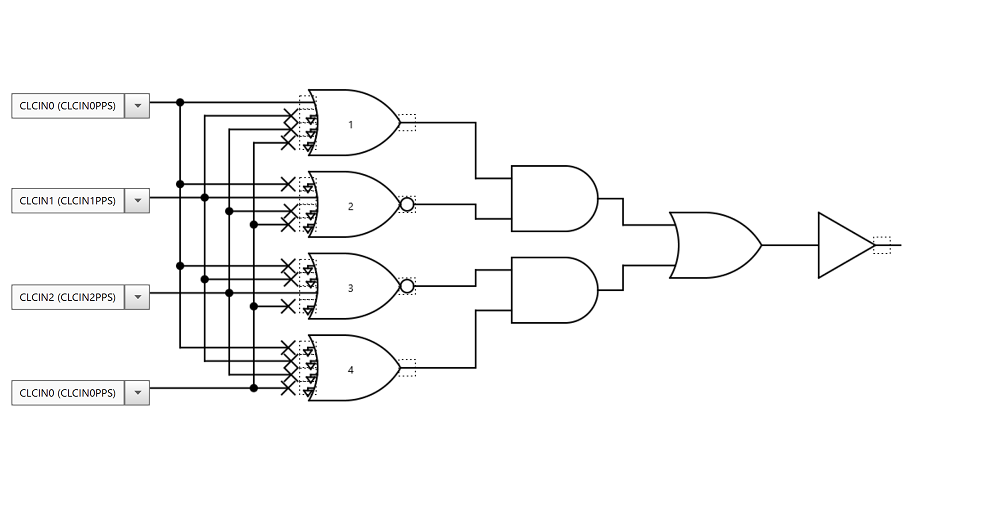

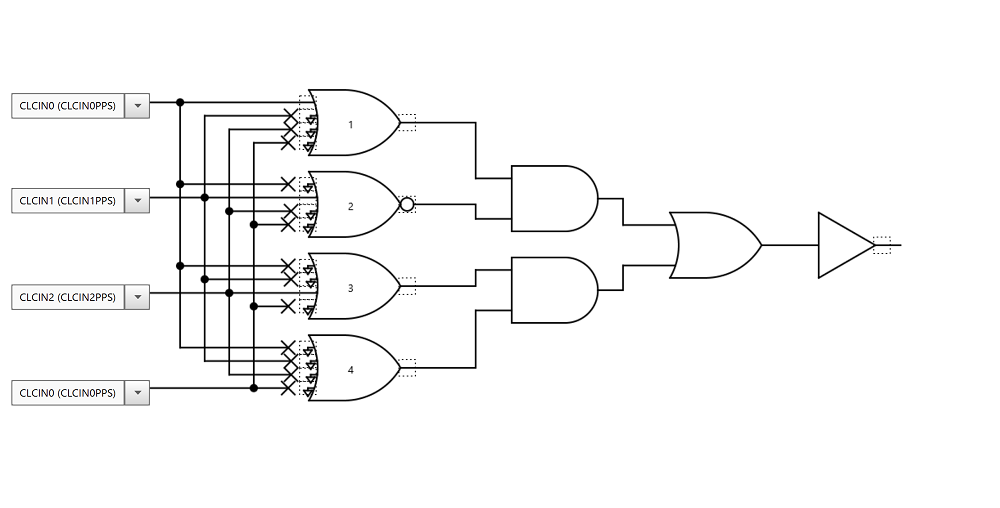

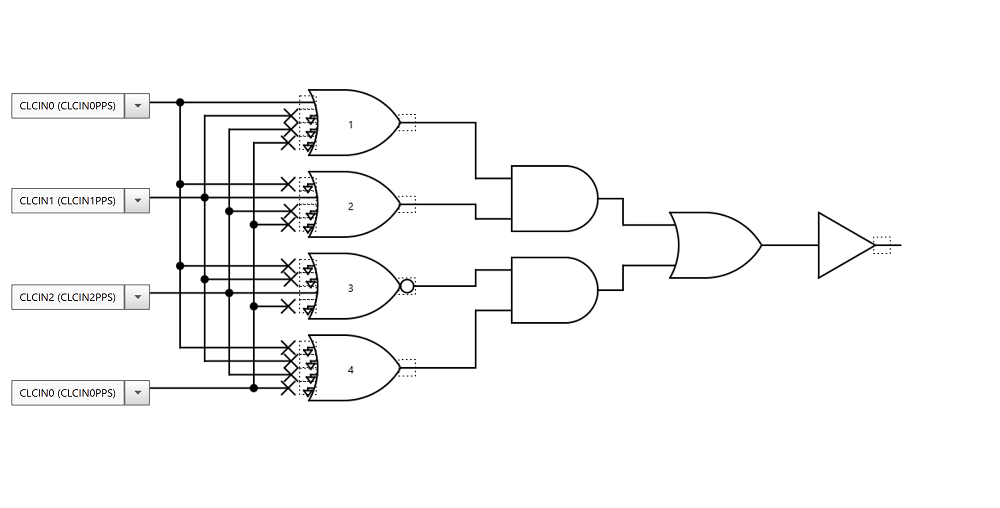

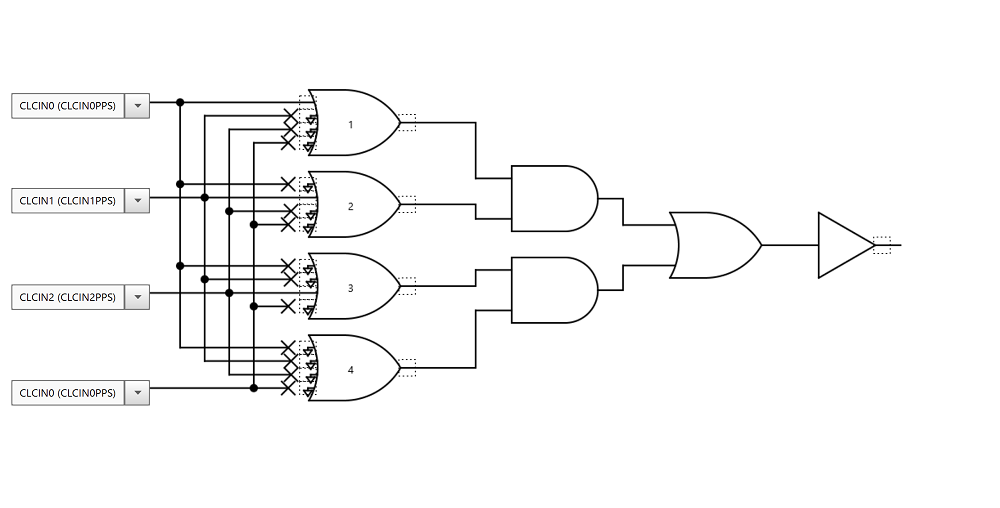

In the previous example, four CLCs were used to implement a 2-to-4 binary encoder in hardware. The following example will demonstrate how to implement 3-to-8 binary decoder using the same principals. Table 4-1 below shows the truth table for the 3-to-8 binary decoder, and Figure 4-1 illustrates the resulting circuit that should be implemented using CLCs, based on the derived Boolean expressions. MCC was used to setup the CLC modules for this application, and the configuration settings can be found in the figures below. The configuration code can be found in 3-to-8 Binary Decoder Initialization Code.

| A2 | A1 | A0 | Y7 | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0 |

|---|---|---|---|---|---|---|---|---|---|---|

0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

3-to-8 Binary Decoder Initialization Code

/*This code block configures the CLCs

for 3-to-8 Binary Decoder.

*/

void CLC1_Initialize(void) {

CLCSELECT = 0x00; // SLCT 0

CLCnPOL = 0x07; // Gate and CLCnOUT Output polarity Selection

CLCnSEL0 = 0x00; // D1S CLCIN0 (CLCIN0PPS)

CLCnSEL1 = 0x01; // D2S CLCIN1 (CLCIN1PPS)

CLCnSEL2 = 0x02; // D3S CLCIN2 (CLCIN2PPS)

CLCnSEL3 = 0x00; // D4S CLCIN0 (CLCIN0PPS)

CLCnGLS0 = 0x02; // CLCn Gate 1 Logic Selection

CLCnGLS1 = 0x08; // CLCn Gate 2 Logic Selection

CLCnGLS2 = 0x08; // CLCn Gate 3 Logic Selection

CLCnGLS3 = 0x00; // CLCn Gate 4 Logic Selection

CLCDATA = 0x00; // CLC1OUT 0

CLCnCON = 0x80; // EN enabled; INTN disabled; INTP disabled; MODE AND-OR

}

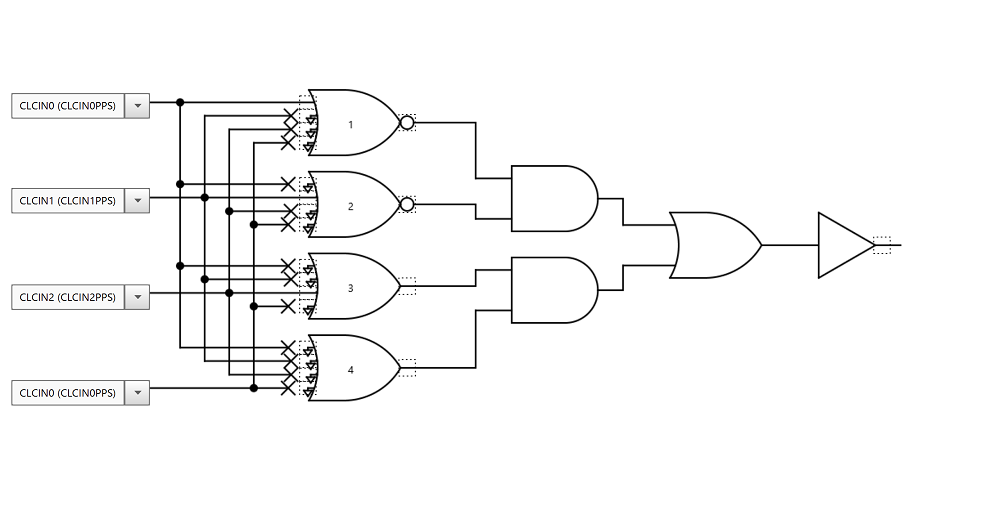

void CLC2_Initialize(void) {

CLCSELECT = 0x01; // SLCT 1

CLCnPOL = 0x03; // Gate and CLCnOUT Output polarity Selection

CLCnSEL0 = 0x00; // D1S CLCIN0 (CLCIN0PPS)

CLCnSEL1 = 0x01; // D2S CLCIN1 (CLCIN1PPS)

CLCnSEL2 = 0x02; // D3S CLCIN2 (CLCIN2PPS)

CLCnSEL3 = 0x00; // D4S CLCIN0 (CLCIN0PPS)

CLCnGLS0 = 0x02; // CLCn Gate 1 Logic Selection

CLCnGLS1 = 0x08; // CLCn Gate 2 Logic Selection

CLCnGLS2 = 0x20; // CLCn Gate 3 Logic Selection

CLCnGLS3 = 0x00; // CLCn Gate 4 Logic Selection

CLCDATA = 0x00; // CLC2OUT 0

CLCnCON = 0x80; // EN enabled; INTN disabled; INTP disabled; MODE AND-OR

}

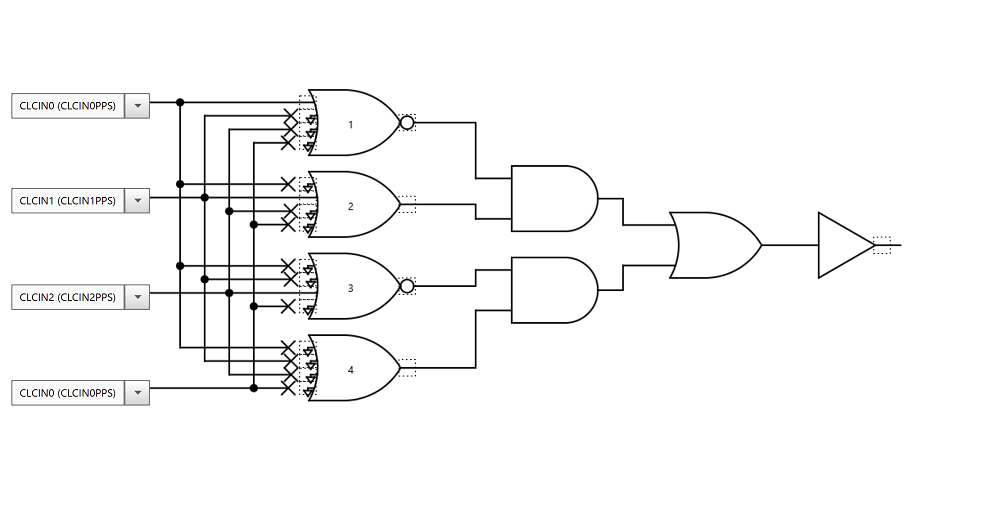

void CLC3_Initialize(void) {

CLCSELECT = 0x02; // SLCT 2

CLCnPOL = 0x05; // Gate and CLCnOUT Output polarity Selection

CLCnSEL0 = 0x00; // D1S CLCIN0 (CLCIN0PPS)

CLCnSEL1 = 0x01; // D2S CLCIN1 (CLCIN1PPS)

CLCnSEL2 = 0x02; // D3S CLCIN2 (CLCIN2PPS)

CLCnSEL3 = 0x00; // D4S CLCIN0 (CLCIN0PPS)

CLCnGLS0 = 0x02; // CLCn Gate 1 Logic Selection

CLCnGLS1 = 0x08; // CLCn Gate 2 Logic Selection

CLCnGLS2 = 0x20; // CLCn Gate 3 Logic Selection

CLCnGLS3 = 0x00; // CLCn Gate 4 Logic Selection

CLCDATA = 0x00; // CLC3OUT 0

CLCnCON = 0x80; // EN enabled; INTN disabled; INTP disabled; MODE AND-OR

}

void CLC4_Initialize(void) {

CLCSELECT = 0x03; // SLCT 3

CLCnPOL = 0x01; // Gate and CLCnOUT Output polarity Selection

CLCnSEL0 = 0x00; // D1S CLCIN0 (CLCIN0PPS)

CLCnSEL1 = 0x01; // D2S CLCIN1 (CLCIN1PPS)

CLCnSEL2 = 0x02; // D3S CLCIN2 (CLCIN2PPS)

CLCnSEL3 = 0x00; // D4S CLCIN0 (CLCIN0PPS)

CLCnGLS0 = 0x02; // CLCn Gate 1 Logic Selection

CLCnGLS1 = 0x08; // CLCn Gate 2 Logic Selection

CLCnGLS2 = 0x20; // CLCn Gate 3 Logic Selection

CLCnGLS3 = 0x00; // CLCn Gate 4 Logic Selection

CLCDATA = 0x00; // CLC4OUT 0

CLCnCON = 0x80; // EN enabled; INTN disabled; INTP disabled; MODE AND-OR

}

void CLC5_Initialize(void) {

CLCSELECT = 0x04; // SLCT 4

CLCnPOL = 0x06; // Gate and CLCnOUT Output polarity Selection

CLCnSEL0 = 0x00; // D1S CLCIN0 (CLCIN0PPS)

CLCnSEL1 = 0x01; // D2S CLCIN1 (CLCIN1PPS)

CLCnSEL2 = 0x02; // D3S CLCIN2 (CLCIN2PPS)

CLCnSEL3 = 0x00; // D4S CLCIN0 (CLCIN0PPS)

CLCnGLS0 = 0x02; // CLCn Gate 1 Logic Selection

CLCnGLS1 = 0x08; // CLCn Gate 2 Logic Selection

CLCnGLS2 = 0x20; // CLCn Gate 3 Logic Selection

CLCnGLS3 = 0x00; // CLCn Gate 4 Logic Selection

CLCDATA = 0x00; // CLC5OUT 0

CLCnCON = 0x80; // EN enabled; INTN disabled; INTP disabled; MODE AND-OR

}

void CLC6_Initialize(void) {

CLCSELECT = 0x05; // SLCT 5

CLCnPOL = 0x02; // Gate and CLCnOUT Output polarity Selection

CLCnSEL0 = 0x00; // D1S CLCIN0 (CLCIN0PPS)

CLCnSEL1 = 0x01; // D2S CLCIN1 (CLCIN1PPS)

CLCnSEL2 = 0x02; // D3S CLCIN2 (CLCIN2PPS)

CLCnSEL3 = 0x00; // D4S CLCIN0 (CLCIN0PPS)

CLCnGLS0 = 0x02; // CLCn Gate 1 Logic Selection

CLCnGLS1 = 0x08; // CLCn Gate 2 Logic Selection

CLCnGLS2 = 0x20; // CLCn Gate 3 Logic Selection

CLCnGLS3 = 0x00; // CLCn Gate 4 Logic Selection

CLCDATA = 0x00; // CLC6OUT 0

CLCnCON = 0x80; // EN enabled; INTN disabled; INTP disabled; MODE AND-OR

}

void CLC7_Initialize(void) {

CLCSELECT = 0x06; // SLCT 6;

CLCnPOL = 0x04; // Gate and CLCnOUT Output polarity Selection

CLCnSEL0 = 0x00; // D1S CLCIN0 (CLCIN0PPS);

CLCnSEL1 = 0x01; // D2S CLCIN1 (CLCIN1PPS);

CLCnSEL2 = 0x02; // D3S CLCIN2 (CLCIN2PPS);

CLCnSEL3 = 0x00; // D4S CLCIN0 (CLCIN0PPS);

CLCnGLS0 = 0x02; // CLCn Gate 1 Logic Selection

CLCnGLS1 = 0x08; // CLCn Gate 2 Logic Selection

CLCnGLS2 = 0x20; // CLCn Gate 3 Logic Selection

CLCnGLS3 = 0x00; // CLCn Gate 4 Logic Selection

CLCDATA = 0x00; // CLC7OUT 0;

CLCnCON = 0x80; // EN enabled; INTN disabled; INTP disabled; MODE AND-OR;

}

void CLC8_Initialize(void) {

CLCSELECT = 0x07; // SLCT 7;

CLCnPOL = 0x00; // Gate and CLCnOUT Output polarity Selection

CLCnSEL0 = 0x00; // D1S CLCIN0 (CLCIN0PPS);

CLCnSEL1 = 0x01; // D2S CLCIN1 (CLCIN1PPS);

CLCnSEL2 = 0x02; // D3S CLCIN2 (CLCIN2PPS);

CLCnSEL3 = 0x00; // D4S CLCIN0 (CLCIN0PPS);

CLCnGLS0 = 0x02; // CLCn Gate 1 Logic Selection

CLCnGLS1 = 0x08; // CLCn Gate 2 Logic Selection

CLCnGLS2 = 0x20; // CLCn Gate 3 Logic Selection

CLCnGLS3 = 0x00; // CLCn Gate 4 Logic Selection

CLCDATA = 0x00; // CLC8OUT 0;

CLCnCON = 0x80; // EN enabled; INTN disabled; INTP disabled; MODE AND-OR;

}