7.5 Changing Output Port Capacitance

Output propagation delay is affected by both the capacitive loading on the board and the I/O standard.

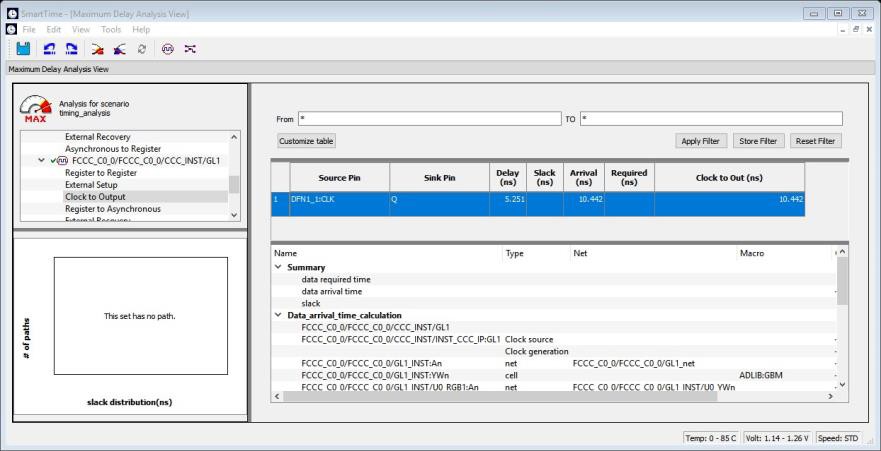

To change the output port capacitance and view the effect of this change in SmartTime Timing Analyzer, see the following example. The following figure shows a delay of 6.603 ns from DFN1 to output port Q based on the default loading of 5 pF.

If your board has an output capacitance of 15 pf on Q, perform the following steps to update the timing number.

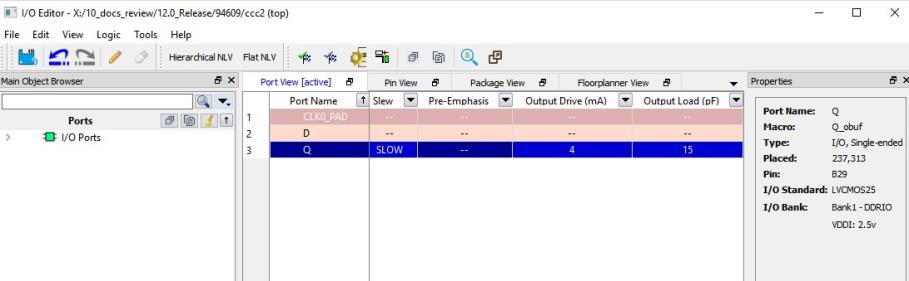

- Open the I/O Attribute Editor and change the output load to 15 pf.

- Select File > Save.

- Select File > Close.

- Open the SmartTime Timing Analyzer and confirm that the Clock to Output delay changed to 5.952 ns.