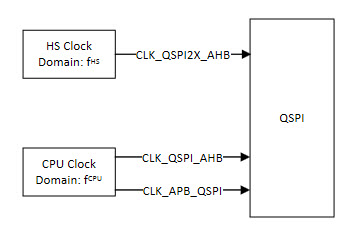

37.5.3 Clocks

The QSPI bus clock (CLK_QSPI_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK_QSPI_APB can be found in the Peripheral Clock Masking section in the MCLK chapter.

An AHB clock (CLK_QSPI_AHB) is required to clock the QSPI. This clock can be enabled and disabled in the Main Clock module, and the default state of CLK_QSPI_AHB can be found in the Peripheral Clock Masking section in the MCLK chapter.

CLK_QSPI_APB, CLK_QSPI_AHB, and CLK_QSPI2X_AHB, respectively, are all synchronous, but can be divided by a prescaler and may run even when the module clock is turned off.