2.1 Power Supply

(Ask a Question)In power supply design, the target impedance of the power planes must be known. The target impedance varies based on the design. This helps in planning the requirement of the number of decoupling capacitors based on the target impedance. The number of decoupling capacitors varies based on the design.

Complex FPGA designs have increasing amounts of current transients switching across the power bus. Simultaneously switching outputs (SSO) contribute a major share of instantaneous current issues. Decoupling is necessary to prevent the instantaneous currents. Decoupling is only effective when inductance is minimized. Low inductance decoupling provides localized high frequency energy to decouple noise from the switching currents of the device power bus. This is most effective when capacitors are in close proximity to the device. Some of these high-frequency de-coupling capacitors must be placed directly under the FPGA or on single side. These capacitors must be placed close to the power and ground pins of the device and routed with thick trace.

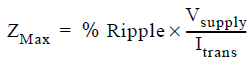

To calculate the number of decoupling capacitors, it is important to know the target impedance of the power plane. Target impedance is calculated as follows:

Where,

Vsupply: Supply voltage of the power plane.

% Ripple: Percentage of ripples that is allowed on the power plane. See DS0128: IGLOO2 and SmartFusion2 Datasheet for more information about ripple in Recommended Operating Conditions table.

Itrans: Transient current drawn on the power plane. The transient current is half of the maximum current. Maximum current is taken from the power calculator sheet.

Zmax: Target impedance of the plane.

Subsequent sections of this document, display simulation results based on target impedance calculated using preceding equations. Microchip strongly recommends calculating the target impedance and performing simulations for the impedance profile of the power plane. These simulations help in optimizing the decoupling capacitors to reduce the production cost and have the optimal placement. The plane shapes in this document are according to the UG0557: SmartFusion2 SoC FPGA Advanced Development Kit User Guide . This might vary depending on the design. For simulation topology, see Appendix D: Power Integrity Simulation Topology.

SmartFusion2/IGLOO2 power supplies are classified as:

- Core power supply

- I/O power supply

Serializer/deserializer (SerDes) power supply

Double data rate (DDR) power supply

Phase-locked loop (PLL) power supply