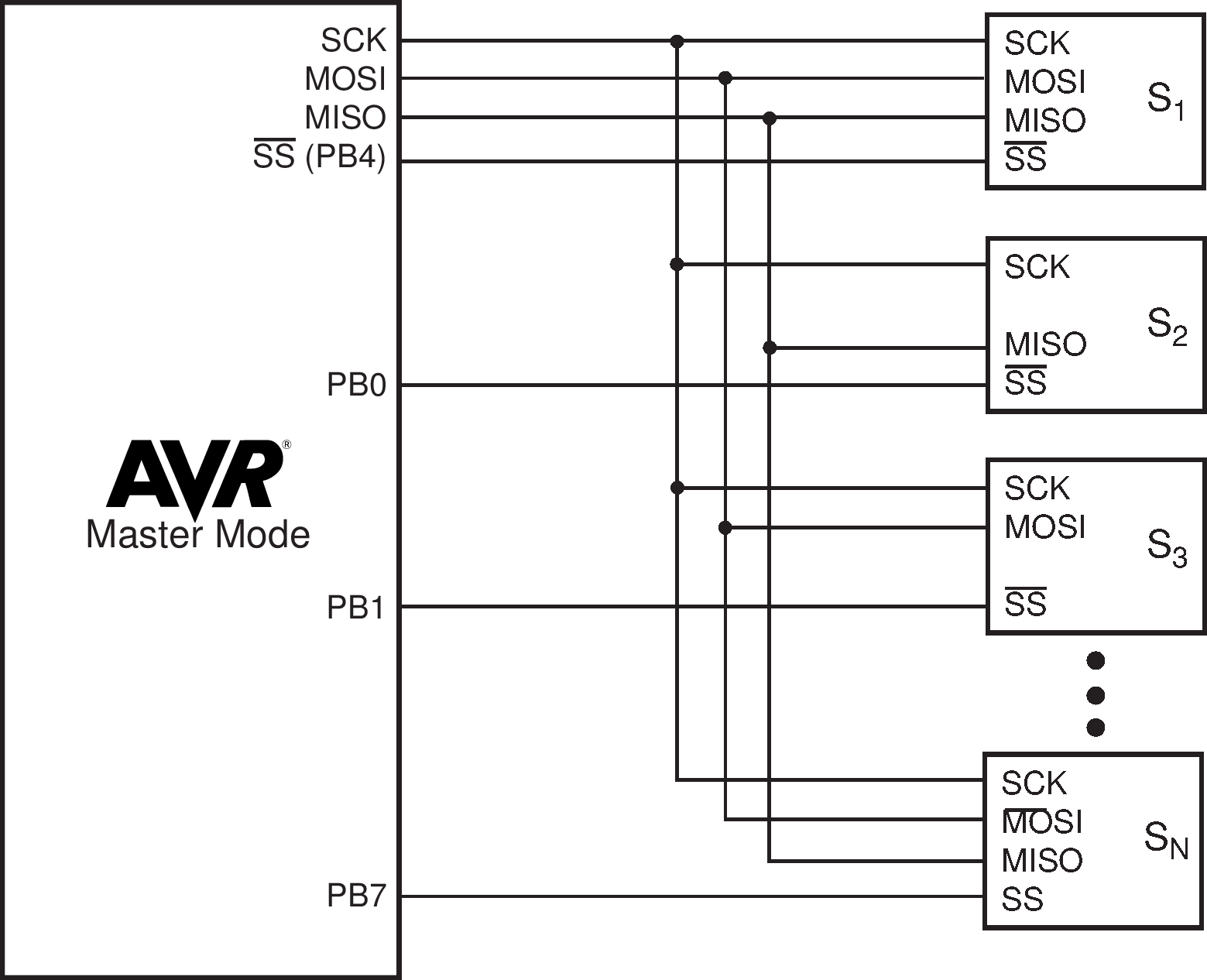

1.3 Multi Slave Systems - SS Pin Functionality

The Slave Select (SS) pin plays a central role in the SPI configuration. Depending on the mode the part is running in and the configuration of this pin, it can be used to activate or deactivate the devices. The SS pin can be compared with a chip select pin which has some extra features.

- The master bit (MSTR) in the SPI Control Register (SPCR) is cleared and the SPI system becomes a slave. The direction of the pins will be switched according to Table 1-2.

- The SPI Interrupt Flag (SPIF) in the SPI Status Register (SPSR) will be set. If the SPI interrupt and the global interrupts are enabled the interrupt routine will be executed.

This can be useful in systems with more than one master to avoid two masters accessing the SPI bus at the same time. If the SS pin is configured as output pin it can be used as a general purpose output pin which does not affect the SPI system.

| Mode | SS Configuration | SS Pin-level | Description |

|---|---|---|---|

| Slave | Always Input | High | Slave deactivated (deselected) |

| Low | Slave activated (selected) | ||

| Master | Input | High | Master activated (selected) |

| Low | Master deactivated, switched to slave mode | ||

| Output | High | Master activated (selected) | |

| Low |

The ability to connect several devices to the same SPI-bus is based on the fact that only one master and only one slave is active at the same time. The MISO, MOSI, and SCK lines of all the other slaves are tristated (configured as input pins of a high impedance with no pullup resistors enabled). A false implementation (e.g. if two slaves are activated at the same time) can cause a driver contention which can lead to a CMOS latchup state and must be avoided. Resistances of 1 to 10kΩ in series with the pins of the SPI can be used to prevent the system from latching up. However this affects the maximum usable data rate, depending on the loading capacitance on the SPI pins.

Unidirectional SPI devices require just the clock line and one of the data lines. The device can use MISO line or the MOSI line depending on its purpose.