2.4.1 Timing Constraints

(Ask a Question)Timing constraints for the designs are required to meet the performance goals of the transceiver interface. Specify timing constraints directly in the SDC or by using the timing constraints editor. The following timing constraints must be methodically introduced into the design. Libero assists by automatically generating timing constraints related to transceiver clock usage.

A component-level SDC file is created for every XCVR instance, which is pulled into the SDC file created for the entire Libero design project as shown in the following example.

CDR reference clock source

Dedicated

create_clock -period <T> [get_pins {LANE<n>/REF_CLK_P}]Fabric

create_clock -period <T> [get_pins {LANE0<n>RX_REF_CLK}]Interface clock

Global

create_clock -period <T> [get_pins {LANE<n>/TX_CLK_G}]

create_clock -period <T> [get_pins {LANE<n>/RX_CLK_G}]Regional or Regional (Deterministic)

create_clock -period <T> [get_pins {LANE<n>/TX_CLK_R}]

create_clock -period <T> [get_pins {LANE<n>/RX_CLK_R}]Global-shared Mode

create_clock -period <T> [get_pins {LANE<n>/TX_CLK_G}]

create_clock -period <T> [get_pins {LANE<n>/RX_CLK_G}]

create_clock -period <T> [get_pins {LANE<n>/TX_CLK_R}]

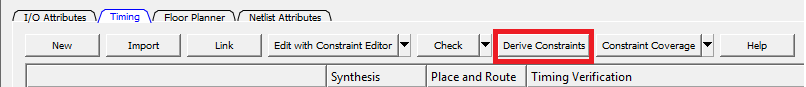

create_clock -period <T> [get_pins {LANE<n>/RX_CLK_R}]Users need to use the Derived SDC file generated by clicking the Derive Constraints in the Timing tab of the Constraint Manager window of Libero SoC software.

The following example shows a Libero project with transceiver.

create_clock -name {REF_CLK_PAD_P} -period 6.4 [ get_ports { REF_CLK_PAD_P } ]

create_clock -name {My_Project_0/my_xcvr_0/PF_XCVR_0/LANE0/TX_CLK_R} -period 16 [ get_pins { My_Project_0/my_xcvr_0/PF_XCVR_0/LANE0/TX_CLK_R } ]

create_clock -name {My_Project_0/my_xcvr_0/PF_XCVR_0/LANE0/RX_CLK_R} -period 16 [ get_pins { My_Project_0/my_xcvr_0/PF_XCVR_0/LANE0/RX_CLK_R } ]

create_clock -name {My_Project_0/my_pll_0_0/pll_xvier_0_0/txpll_isnt_0/DIV_CLK} -period 8 [ get_pins { My_Project_0/my_pll_0_0/my_pll_0_0/txpll

The transceiver can source three different clocks into the fabric—TX_CLK, RX_CLK, and the REFCLK (FAB_REF_CLK). These clock resources have several optional networks such as global or regional routing structures. These global clock resources are susceptible to clock jitter induced by design-specific simultaneous switching activity and the response of the internal device and board-level power distribution network (PDN).

Libero SoC (v2022.1 and later) design software flow is enhanced to automatically apply clock uncertainty constraints to account for the jitter on these clock nets during static timing analysis (STA). The Libero SoC routine analyzes the loaded clock network and uses data driven calculations to apply clock uncertainty that can be anticipated on a typical switching clock net. In addition to global clocks sourced from the transceiver, other FPGA global clock resources are susceptible to clock jitter, including PLLs, DLLs, internal RC Oscillators, and the global nets themselves. See PolarFire Family Clocking Resources User Guide for more information about FPGA clocking resources. Additionally, the device specific Datasheet includes the clock jitter specifications that are used by the Libero SoC automatic clock uncertainty flow.