16.1.7 RAM1K20

(Ask a Question)The RAM1K20 block contains 20,480 (16,896 with ECC) memory bits and is a true dual-port memory. The RAM1K20 memory can also be configured in two-port mode. All read/write operations to the RAM1K20 memory are synchronous. To improve the read-data delay, an optional pipeline register at the output is available. In addition to the feed-through write mode option to enable immediate access to the write-data, RAM1K20 has a Read-before-write option in the dual-port mode. RAM1K20 also includes a Read-enable control for both dual-port and two-port modes. The RAM1K20 memory has two data ports, which can be independently configured in any of the following combination.

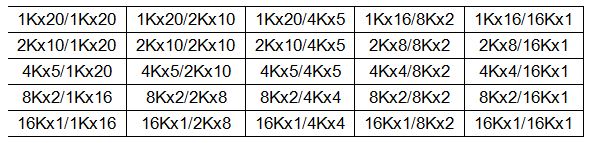

- Non-ECC Dual-Port RAM with the following configurations:

- Any of 1Kx20, 2Kx10, 4Kx5, 8Kx2 or 16Kx1 on each port

- Non-ECC Two-Port RAM with the following configurations:

- Any of 512x40, 1Kx20, 2Kx10, 4Kx5, 8Kx2 or 16Kx1 on each port

- ECC Two-Port RAM with the following configuration:

- 512x33 on both ports

16.1.7.1 Functionality

(Ask a Question)- A RAM1K20 block has 16,896 bits with ECC and 20,480 bits without ECC.

- A RAM1K20 block provides two independent data ports A and B.

- In non-ECC dual-port mode, each port can be independently

configured to any of the following depth/width: 1Kx20, 2Kx10, 4Kx5, 8Kx2 or 16Kx1.

There are 25 unique combinations of non-ECC dual-port aspect ratios:

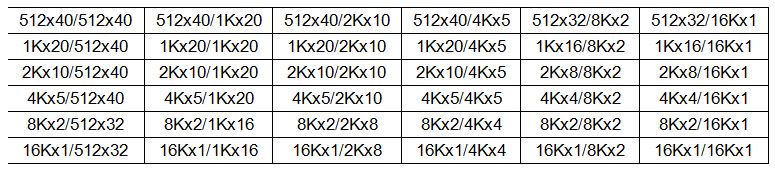

- RAM1K20 also has a two-port mode. In this case, Port A will become the read port and Port B becomes the write port.

- In non-ECC two-port mode, each port can be independently configured to any of the

following depth/width: 512x40, 1Kx20, 2Kx10, 4Kx5, 8Kx2 or 16Kx1. There are 36 unique

combinations of non-ECC two-port aspect ratios:

- RAM1K20 has an ECC two-port mode, for which both ports have word

widths equal to 33 bits. There is one unique combination of ECC two-port aspect

ratio:

512x33/512x33

- RAM1K20 performs synchronous operation for setting up the address as well as writing and reading the data.

- RAM1K20 has a Read-enable control for both dual-port and two-port modes.

- The address, data, block-port select, write-enable and read-enable inputs are registered.

- An optional pipeline register with a separate enable, synchronous-reset and asynchronous-reset is available at the read-data port to improve the clock-to-out delay.

- There is an independent clock for each port. The memory is triggered at the rising edge of the clock.

- The true dual-port mode supports an optional Read-before-write mode or a feed-through write mode, where the write-data also appears on the corresponding read-data port.

- Read from both ports at the same location is allowed.

- Read and write on the same location at the same time results in unknown data to be read. There is no collision prevention or detection. However, correct data is expected to be written into the memory.

- When ECC is enabled, each port of the RAM1K20 memory can raise flags to indicate single-bit-correct and double-bit-detect.

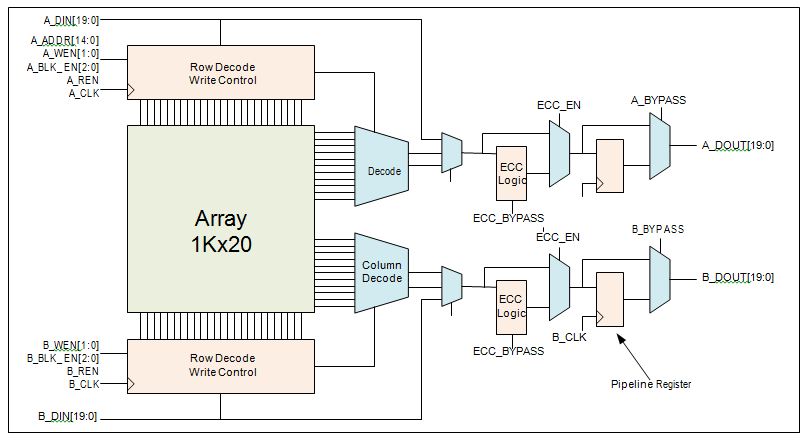

The following figure shows a simplified block diagram of the RAM1K20 memory block. The simplified block illustrates the two independent data ports, ECC, the read-data pipeline registers, read-before-write selection, and the feed-through multiplexors.

| Pin Name | Pin Direction | Type | Description | Polarity |

|---|---|---|---|---|

| A_ADDR[13:0] | Input | Dynamic | Port A address | — |

| A_BLK_EN[2:0] | Input | Dynamic | Port A block selects | High |

| A_CLK | Input | Dynamic | Port A clock | Rising |

| A_DIN[19:0] | Input | Dynamic | Port A write-data | — |

| A_DOUT[19:0] | Output | Dynamic | Port A read-data | — |

| A_WEN[1:0] | Input | Dynamic | Port A write-enables (per byte) | High |

| A_REN | Input | Dynamic | Port A read-enable | High |

| A_WIDTH[2:0] | Input | Static | Port A width/depth mode select | — |

| A_WMODE[1:0] | Input | Static | Port A Read-before-write and Feed-through write selects | High |

| A_BYPASS | Input | Static | Port A pipeline register select | Low |

| A_DOUT_EN | Input | Dynamic | Port A pipeline register enable | High |

| A_DOUT_SRST_N | Input | Dynamic | Port A pipeline register synchronous-reset | Low |

| A_DOUT_ARST_N | Input | Dynamic | Port A pipeline register asynchronous-reset | Low |

| B_ADDR[13:0] | Input | Dynamic | Port B address | — |

| B_BLK_EN[2:0] | Input | Dynamic | Port B block selects | High |

| B_CLK | Input | Dynamic | Port B clock | Rising |

| B_DIN[19:0] | Input | Dynamic | Port B write-data | — |

| B_DOUT[19:0] | Dynamic | Port B read-data | — | |

| B_WEN[1:0] | Input | Dynamic | Port B write-enables (per byte) | High |

| B_REN | Input | Dynamic | Port B read-enable | High |

| B_WIDTH[2:0] | Input | Static | Port B width/depth mode select | — |

| B_WMODE[1:0] | Input | Static | Port B Read-before-write and Feed-through write selects | High |

| B_BYPASS | Input | Static | Port B pipeline register select | Low |

| B_DOUT_EN | Input | Dynamic | Port B pipeline register enable | High |

| B_DOUT_SRST_N | Input | Dynamic | Port B pipeline register synchronous-reset | Low |

| B_DOUT_ARST_N | Input | Dynamic | Port B pipeline register asynchronous-reset | Low |

| ECC_EN | Input | Static | Enable ECC | High |

| ECC_BYPASS | Input | Static | ECC pipeline register select | Low |

| SB_CORRECT | Output | Dynamic | Single-bit correct flag | High |

| DB_DETECT | Output | Dynamic | Double-bit detect flag | High |

| BUSY_FB | Input | Static | Lock access to FCB | High |

| ACCESS_BUSY | Output | Dynamic | Busy signal from FCB | High |

A_WIDTH and B_WIDTH

The following table lists the width/depth mode selections for each port. Two-port mode is in effect when the width of at least one port is greater than 20, and A_WIDTH indicates the read width while B_WIDTH indicates the write width.

| Depth x Width | A_WIDTH/B_WIDTH |

|---|---|

| 16Kx1 | 000 |

| 8Kx2 | 001 |

| 4Kx4, 4Kx5 | 010 |

| 2Kx8, 2Kx10 | 011 |

| 1Kx16, 1Kx20 | 100 |

| 512x32 (Two-port), 512x40 (Two-port), 512x33 (Two-port ECC) | 101 |

A_WEN and B_WEN

The following table lists the write/read control signals for each port. Two-port mode is in effect when the width of at least one port is greater than 20, and read operation is always enabled.

| Depth x Width | A_WEN/B_WEN | Result |

|---|---|---|

| 16Kx1, 8Kx2, 4Kx5, 2Kx10 | x0 | Perform a read operation |

| x1 | Perform a write operation | |

| 1Kx16 | 00 | Perform a read operation |

| 01 | Write [8:5], [3:0] | |

| 10 | Write [18:15], [13:10] | |

| 11 | Write [18:15], [13:10], [8:5], [3:0] | |

| 1Kx20 | 00 | Perform a read operation |

| 01 | Write [9:0] | |

| 10 | Write [19:10] | |

| 11 | Write [19:0] | |

| 512x32 (Two-port write) | B_WEN[0] = 1 | Write B_DIN[8:5], B_DIN[3:0] |

| B_WEN[1] = 1 | Write B_DIN[18:15], B_DIN[13:10] | |

| A_WEN[0] = 1 | Write A_DIN[8:5], A_DIN[3:0] | |

| A_WEN[1] = 1 | Write A_DIN[18:15], A_DIN[13:10] | |

| 512x40 (Two-port write) | B_WEN[0] = 1 | Write B_DIN[9:0] |

| B_WEN[1] = 1 | Write B_DIN[19:10] | |

| A_WEN[0] = 1 | Write A_DIN[9:0] | |

| A_WEN[1] = 1 | Write A_DIN[19:10] | |

| 512x33 (Two-port ECC) | B_WEN[1:0] = 11 | Write B_DIN[16:0] |

| A_WEN[1:0] = 11 | Write A_DIN[15:0] |

A_ADDR and B_ADDR

The following table lists the address buses for the two ports. 14 bits are needed to address the 16K independent locations in x1 mode. In wider modes, fewer address bits are used. The required bits are MSB justified and unused LSB bits must be tied to 0. A_ADDR is synchronized by A_CLK while B_ADDR is synchronized to B_CLK. Two-port mode is in effect when the width of at least one port is greater than 20, and A_ADDR provides the read-address while B_ADDR provides the write-address.

| Depth x Width | A_ADDR/B_ADDR | |

|---|---|---|

| Used Bits | Unused Bits (must be tied to 0) | |

| 16Kx1 | [13:0] | None |

| 8Kx2 | [13:1] | [0] |

| 4Kx4, 4Kx5 | [13:2] | [1:0] |

| 2Kx8, 2Kx10 | [13:3] | [2:0] |

| 1Kx16, 1Kx20 | [13:4] | [3:0] |

| 512x32 (Two-port), 512x40 (Two-port), 512x33 (Two-port ECC) | [13:5] | [4:0] |

A_DIN and B_DIN

The following table lists the data input buses for the two ports. The required bits are LSB justified and unused MSB bits must be tied to 0. Two-port mode is in effect when the width of at least one port is greater than 20, and A_DIN provides the MSB of the write-data while B_DIN provides the LSB of the write-data.

| Depth x Width | A_DIN/B_DIN | |

|---|---|---|

| Used Bits | Unused Bits (must be tied to 0) | |

| 16Kx1 | [0] | [19:1] |

| 8Kx2 | [1:0] | [19:2] |

| 4Kx4 | [3:0] | [19:4] |

| 4Kx5 | [4:0] | [19:5] |

| 2Kx8 | [8:5] is [7:4] [3:0] is [3:0] | [19:9] [4] |

| 2Kx10 | [9:0] | [19:10] |

| 1Kx16 | [18:15] is [15:12] [13:10] is [11:8] [8:5] is [7:4] [3:0] is [3:0] | [19] [14] [9] [4] |

| 1Kx20 | [19:0] | None |

| 512x32 (Two-port write) | A_DIN[18:15] is [31:28] A_DIN[13:10] is [27:24] A_DIN[8:5] is [23:20] A_DIN[3:0] is [19:16] B_DIN[18:15] is [15:12 B_DIN[13:10] is [11:8] B_DIN[8:5] is [7:4] B_DIN[3:0] is [3:0] | A_DIN[19] A_DIN[14] A_DIN[9] A_DIN[4] B_DIN[19] B_DIN[14] B_DIN[9] B_DIN[4] |

| 512x40 (Two-port write) | A_DIN[19:0] is [39:20] B_DIN[19:0] is [19:0 ] | None |

| 512x33 (Two-port ECC) | A_DIN[15:0] is [32:17] B_DIN[16:0] is [16:0 ] | A_DIN[19:16] B_DIN[19:17] |

A_DOUT and B_DOUT

The following table lists the data output buses for the two ports. The required bits are LSB justified. Two-port mode is in effect when the width of at least one port is greater than 20, and A_DOUT provides the MSB of the read-data while B_DOUT provides the LSB of the read-data.

| Depth x Width | A_DOUT/B_DOUT | |

|---|---|---|

| Used Bits | Unused Bits (must be tied to 0) | |

| 16Kx1 | [0] | [19:1] |

| 8Kx2 | [1:0] | [19:2] |

| 4Kx4 | [3:0] | [19:4] |

| 4Kx5 | [4:0] | [19:5] |

| 2Kx8 | [8:5] is [7:4] [3:0] is [3:0] | [19:9] [4] |

| 2Kx10 | [9:0] | [19:10] |

| 1Kx16 | [18:15] is [15:12] [13:10] is [11:8] [8:5] is [7:4] [3:0] is [3:0] | [19] [14] [9] [4] |

| 1Kx20 | [19:0] | None |

| 512x32 (Two-port write) | A_DIN[18:15] is [31:28] A_DIN[13:10] is [27:24] A_DIN[8:5] is [23:20] A_DIN[3:0] is [19:16] B_DIN[18:15] is [15:12 B_DIN[13:10] is [11:8] B_DIN[8:5] is [7:4] B_DIN[3:0] is [3:0] | A_DIN[19] A_DIN[14] A_DIN[9] A_DIN[4] B_DIN[19] B_DIN[14] B_DIN[9] B_DIN[4] |

| 512x40 (Two-port write) | A_DOUT[19:0] is [39:20] B_DOUT[19:0] is [19:0 ] | None |

| 512x33 (Two-port ECC) | A_DOUT15:0] is [32:17] B_DOUT[16:0] is [16:0 ] | A_DOUT[19:16] B_DOUT[19:17] |

A_BLK_EN and B_BLK_EN

The following table lists the block-port select control signals for the two ports. A_BLK is synchronized by A_CLK while B_BLK is synchronized to B_CLK. Two-port mode is in effect when the width of at least one port is greater than 20, and A_BLK_EN controls the read operation while B_BLK_EN controls the write operation.

| Block-port Select Signal | Value | Result |

|---|---|---|

| A_BLK_EN[2:0] | 111 | Perform read or write operation on Port A, unless the width is greater than 20 and a read is performed from both ports A and B. |

| A_BLK_EN[2:0] | Any one bit is 0 | No operation in memory from Port A. Port A read-data will be forced to 0. If the width is greater than 20, the read-data from both ports A and B will be forced to 0. |

| B_BLK_EN[2:0] | 111 | Perform read or write operation on Port B, unless the width is greater than 20 and a write is performed to both ports A and B. |

| B_BLK_EN[2:0] | Any one bit is 0 | No operation in memory from Port B. Port B read-data will be forced to 0, unless the width is greater than 20 and write operation to both ports A and B is gated. |

A_WMODE and B_WMODE

In true dual-port write mode, each port has a feed-through write or read-before-write option.

- Logic 00 = Read-data port holds the previous value.

- Logic 01 = Feed-through, that is write-data appears on the corresponding read-data port. This setting is invalid when the width of at least one port is greater than 20 and the two-port mode is in effect.

- Logic 10 = Read-before-write, that is previous content of the memory

appears on the corresponding read-data port before it is overwritten. This setting is

invalid when the width of at least one port is greater than 20 and the two-port mode is

in effect.

A_CLK and B_CLK

All signals in ports A and B are synchronous to the corresponding port clock. All address, data, block-port select, write-enable and read-enable inputs must be set up before the rising edge of the clock. The read or write operation begins with the rising edge. Two-port mode is in effect when the width of at least one port is greater than 20, and A_CLK provides the read clock while B_CLK provides the write clock.

A_REN and B_REN

Enables read operation from the memory on the corresponding port. Two-port read mode is in effect when the width of port A is greater than 20, and A_REN controls the read operation.

Read-data Pipeline Register Control Signals

A_BYPASS and B_BYPASS A_DOUT_EN and B_DOUT_EN A_DOUT_SRST_N and B_DOUT_SRST_N A_DOUT_ARST_N and B_DOUT_ARST_N

Two-port mode is in effect when the width of at least one port is greater than 20, and the A_DOUT register signals control both the MSB and LSB of the read-data, and the B_DOUT register signals are “don’t-cares”.

The following table describes the functionality of the control signals on the A_DOUT and B_DOUT pipeline registers.

| ARST_N | _BYPASS | _CLK | _EN | _SRST_N | D | Qn+1 |

|---|---|---|---|---|---|---|

| 0 | X | X | X | X | X | 0 |

| 1 | 0 | Not rising | X | X | X | Qn |

| 1 | 0 | ? | 0 | X | X | Qn |

| 1 | 0 | ? | 1 | 0 | X | 0 |

| 1 | 0 | ? | 1 | 1 | D | D |

| 1 | 1 | X | X | X | D | D |

ECC_EN and ECC_BYPASS

ECC operation is only allowed in Two-port mode and the width of both ports is greater than 20.

- ECC_EN = 0: Disable ECC.

- ECC_EN = 1, ECC_BYPASS= 0: Enable ECC Pipelined.

- ECC Pipelined mode inserts an additional clock cycle to Read-data.

- In addition, Write-feed-thru and Read-before-write modes add another clock cycle to Read- data.

- ECC_EN = 1, ECC_BYPASS= 1: Enable ECC Non-pipelined.

SB_CORRECT and DB_DETECT

Error detection and correction flags become available when ECC operation is enabled in Two-port mode and the width of both ports is greater than 20. The following table describes the functionality of the error detection and correction flags.

| DB_DETECT | SB_CORRECT | Flag |

|---|---|---|

| 0 | 0 | No errors have been detected. |

| 0 | 1 | A single bit error has been detected and corrected in the data output. |

| 1 | 1 | Multiple bit errors have been detected, but have not been corrected. |

BUSY_FB

Control signal, when 1 locks the entire RAM1K20 memory from being accessed by the FCB.

ACCESS_BUSY

This output indicates that the RAM1K20 memory is being accessed by the FCB.