16.1.5 Special

(Ask a Question)16.1.5.1 FCEND_BUFF

(Ask a Question)| Input | Output |

|---|---|

| A | Y |

| A | Y |

|---|---|

| 0 | 0 |

| 1 | 1 |

16.1.5.2 FCINIT_BUFF

(Ask a Question)| Input | Output |

|---|---|

| A | Y |

| A | Y |

|---|---|

| 0 | 0 |

| 1 | 1 |

16.1.5.3 PF_SPI

(Ask a Question)| Port | Direction | Polarity | Description |

|---|---|---|---|

| D_I | Output | — | This port is connected to the SPI DI pin. |

| FAB_SPI_OWNER | Output | High | Indicator to the Fabric SPI-Initiator if the SPI Port is available. |

| CLK_OE | Input | High | Enables the SPI CLK output. |

| CLK_O | Input | — | This port drives the SPI Clock pin. CLK_OE must be HIGH to drive. |

| D_OE | Input | High | Enables the Data output. |

| D_O | Input | — | This port drives the SPI DO pin. D_OE must be HIGH to drive. |

| SS_OE | Input | High | Enables the Target Select output. |

| SS_O | Input | High | This port drives the SPI Target Select (SS) pin. SS_OE must be HIGH to drive. |

| CLK | Output | — | SPI Clock output pin. |

| DI | Input | — | SPI Serial Data input pin. |

| DO | Output | — | SPI Serial Data output pin. |

| SS | Output | High | SPI Target Select output pin. |

| IFACE | Input | High | This port is mapped to the IO_CFG_INTF pin. This pin must be tied to high together with the SC_SPI_EN pin to enable SPI port for the fabric macro to work. |

| FLASH | Input | High | This port is mapped to the SC_SPI_EN pin. This pin must be tied to high together with the IO_CFG_INTF pin to enable the SPI port for fabric macro to work. |

16.1.5.4 SC_STATUS

(Ask a Question)- At simulation time t = 0, set

SUSPEND_EN= 0, andACTIVE= 1. - 0.625 µs after the later of

DEVICE_INIT_DONE= 1 orAUTOCALIB_DONE= 1 is asserted, setSUSPEND_EN= 1, andACTIVE= 0 to indicate that the system controller has entered suspend mode.

| Value | Description |

|---|---|

| 0 | The device is not in avionics mode. |

| 1 | The device is in avionics mode. |

For ACTIVE signal, if SC is in suspend mode, ACTIVE signal must not be asserted.

| Port | On Initiator | On Target | Description | ||||

|---|---|---|---|---|---|---|---|

| Presence | Width | Direction | Presence | Width | Direction | ||

| SUSPEND_EN | Required | 1 | Output | Required | 1 | Input | Asserted when SC is in suspend mode. |

| ACTIVE | Required | 1 | Output | Required | 1 | Input | Asserted when SC is in active mode. |

16.1.5.5 OSC_RC160MHZ

(Ask a Question)The OSC_RC160MHZ oscillator is an RC oscillator that provides a free-running clock of 160 MHz at CLKOUT when OSC_160MHZ_ON is tied HIGH.

16.1.5.6 OSC_RC2MHZ

(Ask a Question)The OSC_RC2MHZ oscillator is an RC oscillator that provides a free-running clock of 2 MHz at CLKOUT when OSC_2MHZ_ON is tied HIGH.

16.1.5.7 LIVE_PROBE_A

(Ask a Question)This is one of the specialized probes. SmartDebug uses the dedicated and specialized probe points built in the FPGA fabric, which significantly accelerates and simplifies the debug process.

16.1.5.8 INIT

(Ask a Question)- FABRIC_POR_N: De-asserted when the fabric is operational.

- PCIE_INIT_DONE: Used by fabric logic to hold PCIe-related fabric logic in reset until the PCIe controller is initialized. PCIE_INIT_DONE is asserted after initializing the PCIe lane instances placed in the PCIe quad. If only XCVR lanes are placed in the PCIe quad, only XCVR_INIT_DONE is asserted.

- RFU[0]: Asserted when the XCVR block is initialized.

- RFU[1]: Asserted when μSRAM is initialized from sNVM.

- RFU[2]: Asserted when μSRAM is initialized from µPROM.

- RFU[3]: Asserted when μSRAM is initialized from SPI.

- RFU[4]: Asserted when SRAM is initialized from sNVM.

- RFU[5]: Asserted when SRAM is initialized from µPROM.

- RFU[6]: Asserted when SRAM is initialized from SPI.

- RFU[7]: Asserted when auto calibration is done.

- SRAM_INIT_DONE: Asserted when the LSRAM blocks are initialized.

- USRAM_INIT_DONE: Asserted when the µSRAM blocks are initialized.

- GPIO_ACTIVE: This signal can be used by user logic to determine if the calibration completes for each I/O banks. # denotes the bank number (0,1, 7, 8, and 9).

- HSIO_ACTIVE: This signal can be used to monitor if there is VDDI power loss on specific I/O banks. This is an output signal from the INIT_MONITOR IP if any of the corresponding bank is selected. # denotes the bank number (0,1, 7, 8, and 9).

16.1.5.9 LANECTRL

(Ask a Question)The lane controller handles the complex operations necessary for the high-speed interfaces, such as DDR memory and CDR interfaces. To bridge the lane clock to the high-speed I/O clock, the lane controller is used to control an I/O FIFO in each IOD. The I/O FIFO interfaces with DDR memory by using the Data Q Strobe (DQS) on the lane clock. The lane controller can also delay the lane clock using a Process, Voltage, and Temperature (PVT)-calculated delay code from the DLL to provide a 90° shift. Certain I/O interfaces require a lane controller to handle the clock-domain that results with higher gear ratios. The lane controller also provides the functionality for the IOD CDR. Using the four phases from the CCC PLL, the lane controller creates eight phases and selects the proper phase for the current input condition with the input data.

16.1.5.10 LANECTRL_BYPASS

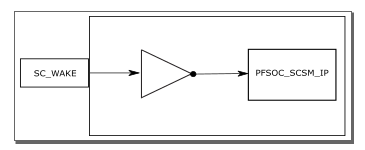

(Ask a Question)16.1.5.11 PFSOC_SCSM

(Ask a Question)The PFSOC_SCSM macro allows a PolarFire SoC device configured with the

System Controller Suspend Mode (SCSM) enabled to support MSS reboots during a normal

device operation. Without this macro, the System Controller:

- Will remain in the suspend mode during normal operation after the initial power-up device initialization and MSS boot completion.

- Will not service subsequent MSS boot requests, even if you reset the MSS.

You must connect the REBOOT_REQUESTED_M2F output of the MSS component to

the SC_WAKE input pin of the PFSOC_SCSM macro. Other

connections are not permitted.

REBOOT_REQUESTED_M2F port in the

MSS configurator, check the Expose Feedback ports to Fabric

option under the Misc tab.With this connection added to your FPGA fabric design, whenever, the MSS

REBOOT_REQUESTED_M2F output is asserted, the System Controller exits SCSM

and processes the pending MSS reboot request. Once the MSS boots, the

REBOOT_REQUESTED_M2F output will deassert and the System Controller

returns to the suspend mode. The System Controller status can be monitored via the

SC_STATUS macro.

PFSOC_SCSM macro only supports the

PolarFire SoC (production device) family. PolarFire SoC Engineering Silicon (ES) devices

are not supported.

Design Rule Checks

Following are the Design Rule Checks (DRCs) for the PFSOC_SCSM

macro.

- Check that the driver is only

MSS REBOOT_REQUESTED_M2F, otherwise thePFSOC_SCSMmacro will error out and stop the flow with the following message:The PFSOC_SCSM primitive macro only supports being driven by the MSS component’s REBOOT_REQUESTED_M2F output. Other drivers are not supported. See the PolarFire SoC Macro Library Guide for more information. - If Suspend is not enabled, and

the

PFSOC_SCSMis instantiated, a warning is issued in the Export Design Initialization Data and Memory Report file.The PFSOC_SCSM macro is instantiated in the design, but System Controller Suspend Mode is not enabled. This macro is intended for use with System Controller Suspend Mode. See the PolarFire SoC Macro Library Guide for more information. - If Suspend is enabled, and the

MSS is used, but the

PFSOC_SCSMmacro is not instantiated, a warning is issued in the Export Design Initialization Data and Memory Report file.The PFSOC_SCSM macro is not instantiated even though System Controller Suspend Mode is enabled and the MSS component is instantiated. The system controller will not be available to process MSS reboot requests during operation. See the PolarFire SoC Macro Library Guide for more information. - The

PFSOC_SCSMmacro is visible only for the PolarFire SoC designs. This macro is required for the PolarFire SoC designs using the MSS component and enabling System Controller Suspend Mode (SCSM). When not used in the PolarFire SoC designs, Libero ties the input to the System Controller, to a static1. - If an ES device or a PolarFire

family is selected, the

PFSOC_SCSMmacro will error out and stop the flow in compile with the following error message, as only production PolarFireSoC devices are supported.CMPPF_026: This design has one or more instances of the PFSOC_SCSM macro which is not supported for the device in use. Before compiling, this macro(s) must be removed from the design.