20.2.2.3.5 DDR Memory

(Ask a Question)Select the required DDR type from the DDR Memory Type pull-down. The DDR configuration options are available on the DDR Topology, DDR Controller, DDR Memory Initialization, and DDR Memory Timing tabs (see the following figure).

For more information about the architecture and functional blocks of MSS DDR Controller, see PolarFire SoC FPGA MSS Technical Reference Manual . This section describes the options available in the tab for configuring MSS DDR Controller.

- For DDR3 and DDR4, the COMPONENT, UDIMM, RDIMM, LRDIMM, and SODIMM memory formats are supported.

- For LPDDR3/4, only the COMPONENT memory format is supported.

- Enable the Lock Down DDR I/Os option to lock all the DDR I/Os.

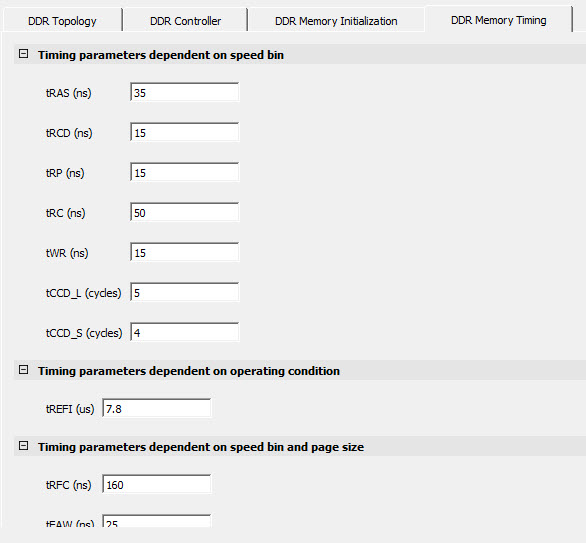

- Configure the DDR parameters according to the data sheet from the DDR vendor.

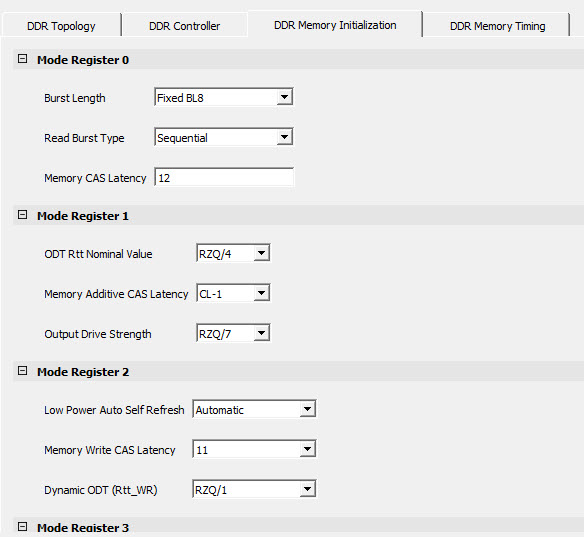

The DDR Memory Initialization tab controls the DDR mode register configuration according to the JEDEC specification. In the PolarFire SoC FPGA DDR architecture, these parameters are passed to the start-up code running on the E51 monitor core, which then performs the DDR initialization sequence and configures the mode registers.

The Advanced tab controls the self refresh mode parameters (idle time to self refresh and clock disable in self refresh).