15.3.3 Debugging

(Ask a Question)This topic introduces how to use the debugger to gather the device status and to view the diagnostics.

15.3.3.1 Common Debug Elements

(Ask a Question)15.3.3.1.1 Debug FPGA Array

(Ask a Question)In the Debug FPGA Array dialog box, you can view your Live Probes, Active Probes, Memory Blocks, and Insert Probes (Probe Insertion) in either the Hierarchical View or the Netlist View.

The Debug FPGA Array dialog box includes the following four tabs:

It also includes the FPGA Hardware Breakpoint (FHB) controls, consisting of the following tabs:

15.3.3.1.2 Hierarchical View

(Ask a Question)The Hierarchical View lets you view the instance level hierarchy of the design programmed on the device and select the signals to add to the Live Probes, Active Probes, and Probe Insertion tabs in the Debug FPGA Array dialog box. Logical and physical Memory Blocks can also be selected.

- Filter: In Live Probes, Active Probes, Memory Blocks, and the Probe Insertion UI, a search option is available in the Hierarchical View. You can use wildcard characters such as * or ? in the search column for wildcard matching. Probe points of leaf level instances resulting from a search pattern can only be added to Live Probes, Active Probes, and the Probe Insertion UI. You cannot add instances of search results in the Hierarchical View.

- Instance(s): Displays the probe points available at the instance level.

- Primitives: Displays the lowest level of probe-able points in the hierarchy for the corresponding component such as leaf cells (hard macros on the device).

- Highlight Selected: Check to highlight selected active, live, or probe insertion probes in their respective tabs within the Hierarchical View. By default, this check box is checked.

You can expand the hierarchy tree to see lower level logic. Signals with the same name are grouped automatically into a bus that is presented at instance level in the instance tree.

The probe points can be added by selecting any instance or the leaf level instance in the Hierarchical View. Adding an instance adds all the probe-able points available in the instance to Live Probes, Active Probes, and Probe Insertion.

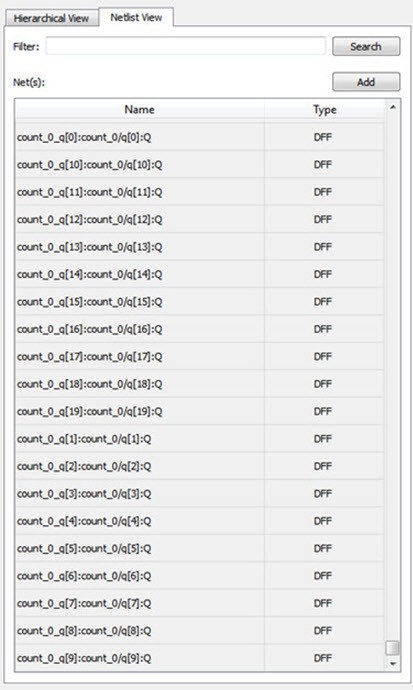

15.3.3.1.3 Netlist View

(Ask a Question)The Netlist View displays a flattened net view of all the probe-able points present in the design, along with the associated cell type.

A search option is available in the Netlist View for Live Probes, Active Probes, and Probe Insertion. You can use wildcard characters such as * or ? in the search column for wildcard matching.

15.3.3.1.4 Live Probes

(Ask a Question)The same circuitry for programming the flash switches that have access to these points at the DFFs of every LE is re-purposed for debugging. SmartDebug controls these signal points with the JTAG interface to either allow asynchronous reads from and writes to these DFFs, or to use an additional muxing circuit that allows two signal points to be rerouted to special pins called "channels." These signal points are I/O pads present on the FPGA boards that could be used to connect to the oscilloscope to monitor dynamic signals.

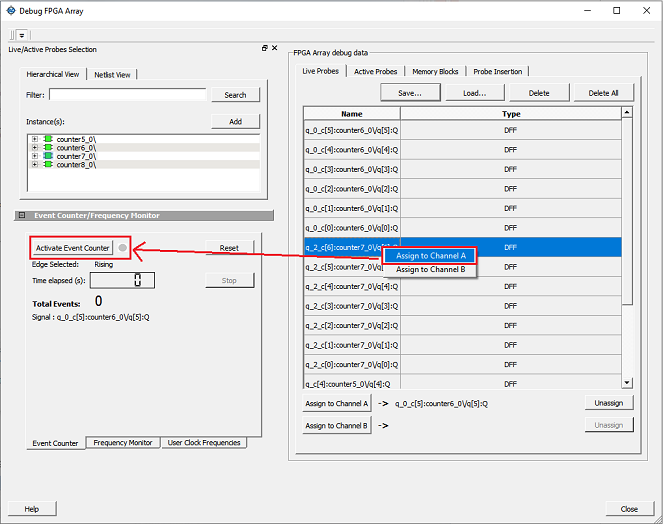

Two probe channels are available for PolarFire, SmartFusion 2, and IGLOO 2 devices. When a probe name is selected, it can be assigned to any channel. Both probes can be assigned or unassigned independently.

To assign a probe to a channel, either:

- Right click a probe in the table and choose Assign to Channel for PolarFire and PolarFire SoC or Assign to probe read data pin for RTG4.

- Click Assign to Channel for PolarFire and PolarFire SoC or Assign to probe read data pin for RTG4 to assign the probe selected in the table to the channel.

When the assignment is complete, the probe name appears to the right of the button for that channel, and SmartDebug configures the channel I/Os to monitor the desired probe points. Because there are only two channels, a maximum of two internal signals can be probed simultaneously.

Click Unassign Channels for PolarFire and PolarFire SoC or Unassign probe read data pin for RTG4 to clear the live probe names to the right of the channel buttons and discontinue the live probe function during debug.

The Save button saves the list of live probes currently shown in the SmartDebug Live Probe UI to file. The Load button loads the list of live probes from a file to SmartDebug Live Probe UI.

During save or load, check whether the appropriate signals saved or loaded match the signals in SmartDebug Live Probe UI and in the saved file.

Live Probes in Demo Mode

You can assign and unassign Live Probes Channel A and Channel B in Demo Mode.

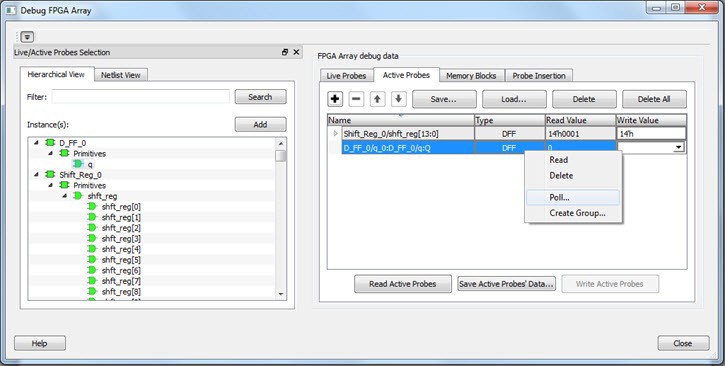

15.3.3.1.5 Active Probes

(Ask a Question)The active probes design debug option reads and writes to one or many probe points in the design through JTAG. This option uses the same circuitry that is used for programming the fabric. It is also non-intrusive and works asynchronously with the design clocks. In PolarFire, 18 DFFs are read at a time from the device that are physically placed adjacent to each other in the fabric. If you want to debug the design related to timing issue, then it is recommended to stop the design clocks. The FHB feature can be used to stop the design clock and then probe all the DFFs in the design.

In the left pane of the Active Probes tab, all available Probe Points are listed in instance-level hierarchy in the Hierarchical View. All Probe Names are listed with the Name and Type (which is the physical location of the flip-flop) in the Netlist View.

Select probe points from the Hierarchical View or Netlist View, right click and choose Add to add them to the Active Probes UI. You can also add the selected probe points by clicking the Add button. The probes list can be filtered with the Filter box.

Use the following options in the Write Value column to modify the probe signal added to the SmartDebug FPGA Array debug data dialog box:

- Drop-down menu with values 0 and 1 for individual probe signals

- Editable field to enter data in hex or binary for a probe group or a bus

Active Probes in Demo Mode

In the demo mode, a temporary probe data file with details of current and previous values of probes added in the Active Probes tab is created in the designer folder. The write values of probes are updated to this file, and the GUI is updated with values from this file when you click Write Active Probes. Data is read from this file when you click Read Active Probes. If there is no existing data for a probe in the file, the read value displays all 0s. The value is updated based on your changes.

15.3.3.1.6 Probe Grouping (Active Probes Only)

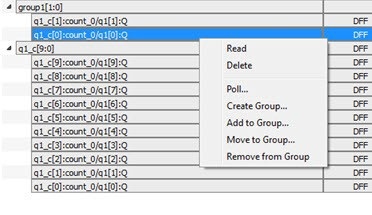

(Ask a Question)During the debug cycle of the design, designers often want to examine the different signals. In large designs, there can be many signals to manage. The Probe Grouping feature assists in comprehending multiple signals as a single entity. This feature is applicable to Active Probes only. Probe nets with the same name are automatically grouped in a bus when they are added to the Active Probes tab. Custom probe groups can also be created by manually selecting probe nets of a different name and adding them into the group.

The Active Probes tab provides the following options for probe points that are added from the Hierarchical View/Netlist View:

- Display bus name. An automatically generated bus name cannot be modified. Only custom bus names can be modified.

- Expand/collapse bus or probe group

- Move Up/Down the signal, bus, or probe group

- Save (Active Probes list)

- Load (already saved Active Probes list)

- Delete (applicable to a single probe point added to the Active Probes tab)

- Delete All (deletes all probe points added to the Active Probes tab)

Green entries in the Write Value column indicate that the operation was successful. Blue entries in the Read Value column indicate values that have changed since the last read.

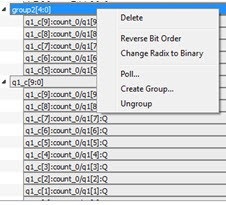

- Create Group, Add/Move signals to Group, Remove signals from Group

- Ungroup

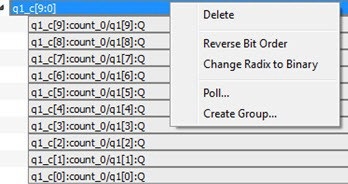

- Reverse bit order, Change Radix for a bus or probe group

- Read, Write, or Delete the signal or bus or probe group

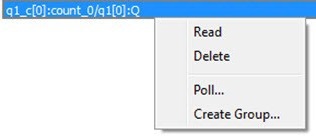

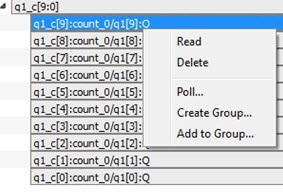

Context Menu of Probe Points Added to the Active Probes UI

(Ask a Question)When you right click a signal or bus, you will see the following menu options:

| Situation | Options | User Interface |

|---|---|---|

| For individual signals that are not part of a probe group or bus |

|  |

| For individual signals in a probe group |

|  |

| For individual signals in a bus |

|  |

| For a bus |

|  |

| For a probe group |

|  |

Differences Between a Bus and a Probe Group

(Ask a Question)In addition, certain operations are also restricted to the member of a bus, whereas they are allowed in a probe group.

The following operations are not allowed in a bus.

- Move to Group: Moving a signal to a probe group

- Remove from Group: Removing a signal from a probe group

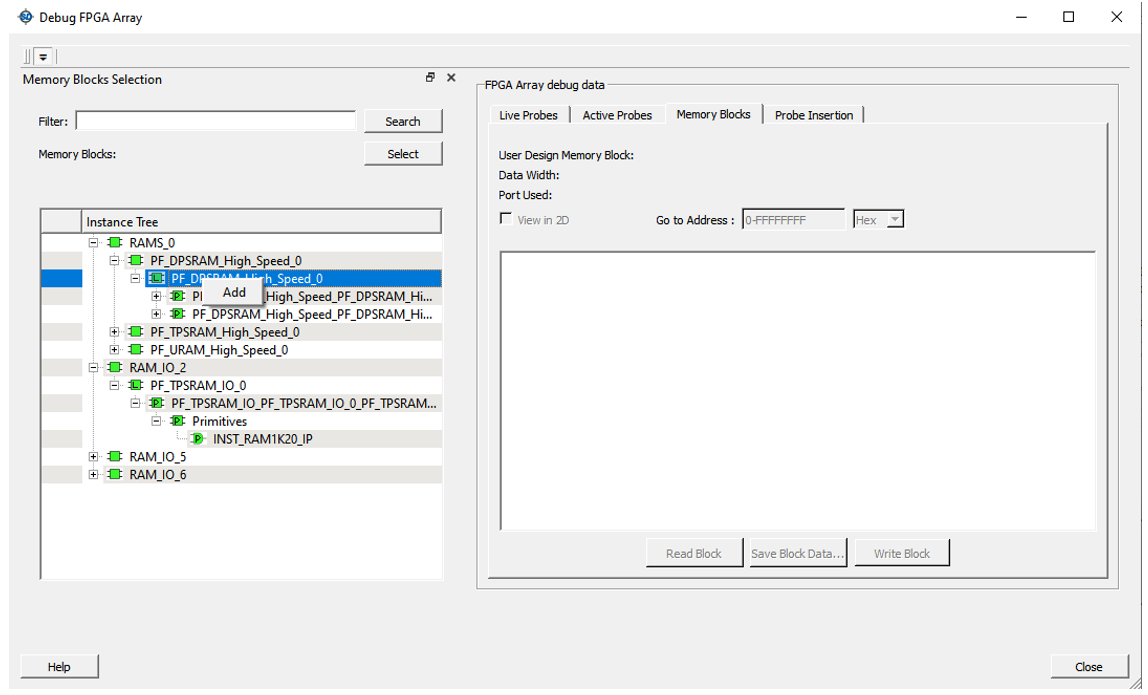

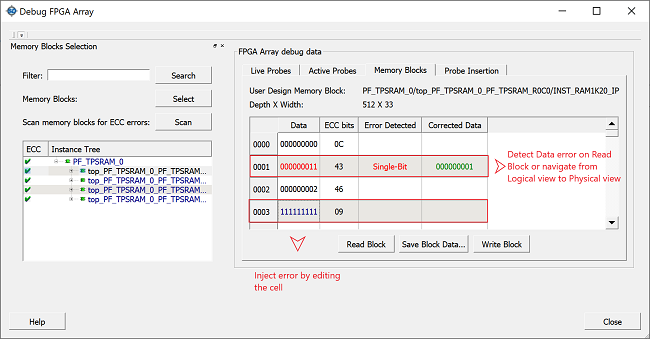

15.3.3.1.7 Memory Blocks

(Ask a Question)Memory debug accesses the RAMs present in the fabric. Large SRAM or micro SRAM can be accessed through JTAG. SmartDebug takes the access from the user interface via fabric control bus (FCB) to read and write into the locations. Once the read operation is performed, the interface is relinquished and given back to the user interface. During this operation, any data read may be outdated or unreliable and you may not be able to access the memory until the SmartDebug has finished its operation.

The Memory Blocks tab in the Debug FPGA Array dialog box shows the hierarchical view of all memory blocks in the design. You determine the depth and width of blocks shown in the logical view in SmartDesign, RTL, or IP cores using memory blocks.

- You cannot access RAM when SmartDebug accesses RAM blocks.

- You cannot access RAM is not

accessible during a read or write operation.

- During a single location write, the RAM block is not accessible. If multiple locations are written, the RAM block is accessed and released for each write.

- When each write is completed, access returns to the user, so the access time is a single write operation time.

The following figure shows the hierarchical view of the Memory Blocks tab. You can view logical blocks and physical blocks. Logical blocks are shown with an L (

You can select only one block at a time. You can select and add blocks in the following ways:

- Right click the name of a memory

block and click Add, as shown in the following figure.

Figure 15-70. Adding a Memory Block

- Click a name in the list and then click Select.

- Click a name, drag it to the right, and drop it into the Memory Blocks tab.

- Enter a memory block name in the Filter box and click Search or press Enter. Wildcard search is supported.

A View in 2D check box allows you to toggle between a 1-dimensional or 2-dimensional view of the memory block (default is 2 dimensional). The Go to Address option to the right of the check box allows you to navigate to an offset address location in either hexadecimal or decimal format.

Memory Block Fields

(Ask a Question)The following memory block fields appear in the Memory Blocks tab.

User Design Memory Block

The selected block name appears on the right side. If the block selected is logical, the name from the top of the block is shown.

Data Width

If a block is logical, the depth and width is retrieved from each physical block, consolidated, and displayed.

Values vary with the device family. For PolarFire devices, if the block is physical, the value of "Depth × Width" is 64 × 12 for μSRAM blocks, 16384 × 1, 8192 × 2, 4096 × 5, 2048 × 10, 1024 × 20 for LSRAM blocks, and 512 × 40 (512 × 33 if Error Correcting Code is enabled where 512 × 7 is dedicated for ECC) for Two-Port RAM(TPSRAM) physical block. Corresponding values for other Microchip devices can be found in their respective datasheets.

Port Used

This field is displayed only in the logical block view. Because configurators can have asymmetric ports, memory location can have different widths. The port shown can either be Port A or Port B. For TPSRAM, where both ports are used for reading, Port A is used. This field is hidden for physical blocks, as the values shown will be irrespective of read ports.

Memory Block Views

The following figure shows the Memory Blocks tab fields for a logical block view.

The following figure shows the Memory Blocks tab fields for a physical block view.

Read Block

(Ask a Question)Memory blocks can be read once they are selected. If the block name appears on the right side, the Read Block button is enabled. Click Read Block to read the memory block.

Logical Block Read

A logical block shows three fields. User Design Memory Block and Depth X Width are read-only fields, and the Port Used field has options. If the design uses both ports, Port A and Port B are shown under options. If only one port is used, only that port is shown.

- If the inference flow (RTL – synthesis) is used in the design, the inference guidelines provided by Synopsys have to be followed.

- Because few IPs deviate from inference guidelines, no logical reconstruction is supported.

- If your design has output pins of RAM (A_DOUT and B_DOUT) that have been partially promoted to top, physical blocks corresponding to remaining pins may be optimized. As a result, reconstruction may not be done.

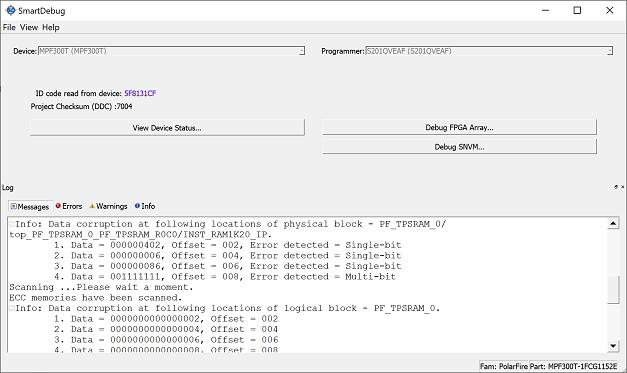

Logical Block Read for ECC-Enabled Blocks (PolarFire, PolarFire SoC, and RTG4)

Two-Port RAMs on PolarFire, PolarFire SoC, and RTG4 devices support Error Correcting Code (ECC) that provides Single Error Correction and Double Error Detection (SECDED). The logical block view for ECC-enabled blocks highlights the data in case any corruption is detected. All erroneous data is highlighted in red. Hover your cursor over the error to display a tooltip that shows the ECC error with the offset details. After the logical block is read, all the physical block data is recorded for navigating to the respective physical block, so you can view the respective physical block without having to read from the device again.

Physical Block Read

When a physical block is selected, only the User Design Memory Block and Depth X Width fields are shown.

Physical Block Read for ECC-Enabled Blocks

Instead of data being shown in a matrix form, ECC-enabled blocks are shown with data internally spread across Port A and Port B. As a result, they are concatenated to show the 33-bit data offset value in a single column. Similarly, ECC bits are concatenated from the two ports and shown in the adjacent column.

The following table describes the columns displayed in the physical block view.

| Column | Description |

|---|---|

| Data | PolarFire and PolarFire SoC devices: 33-bit physical block data

offset value. RTG4 devices: 18-bit physical block data offset value. |

| ECC Bits | PolarFire and PolarFire SoC devices: 7-bit ECC value. RTG4 devices: 6-bit ECC value. |

| Error Detected | Displays identified error type. The error type value displayed can be either Single-Bit or Multi-Bit. |

| Corrected Data | If the error is a single-bit error, then the tool suggests the

corrected data. The suggested data can be copied to the data cell in

order to write into the device. Right click on the corrected data to view an option to copy the data automatically to the Data cell. |

After the block is read, a log is generated and all the erroneous locations are listed. This log is also seen during a physical block read or when navigated from logical block view to physical. The same is true when navigating from physical to logical block view.

Write Block

(Ask a Question)Logical Block Write

A memory block write can be done on each location individually. A logical block shows each location of width. The written format is hexadecimal numbers from 0 to F. Width is shown in bits, and values are shown in hexadecimal format. If an entered value exceeds the maximum value, SmartDebug displays a message showing the range of allowed values.

Logical Block Write for ECC-Enabled Blocks

You can inject error into the logical block by writing onto the location. To verify whether data is corrupted, read on the logical block to highlight the corresponding location.

Physical Block Write

Physical blocks have a fixed width of 129 bits for uSRAM and the maximum value that can be written in hexadecimal format is FFF. Similarly, for LSRAM blocks, a range of values are possible (1, 2, 5, 10, and 20) and the maximum values can be 1, 3, 1F, 3FF, and FFFFF, respectively. If an entered value exceeds the limit, a message shows the range of permitted values that can be entered.

Physical Block Write for ECC-Enabled Blocks

Limitation of Injecting Errors

- An incorrect Single-bit corrected data is suggested.

- Error might not be detected because the ECC calculated for the corrupted data might be the same that ECC calculated originally.

Scan Memory

(Ask a Question)Memory Hierarchy in the Debug FPGA Array window is enhanced to display whether the ECC-enabled memory blocks are corrupted or not by providing a scan option.

Click Scan to scan the ECC-enabled memory blocks for errors. If there are no errors in a memory block, a green tick appears on to the left of memory block name. Otherwise, a red circle indicates that the data is corrupted.

Unsupported Memory Blocks

(Ask a Question)If RTL is used to configure memory blocks, it is recommended that you follow the Microchip RAM block inference guidelines in the application note for your Microchip device (see Related Application Notes below).

SmartDebug may or may not be able to support logical view for memory blocks that are inferred using RTL coding.

Memory Blocks in Demo Mode

(Ask a Question)A temporary memory data file is created in the designer folder for each type of RAM selected. All memory data of all instances of USRAM, LSRAM, and other RAM types is written to their respective data files. The default value of all memory locations is shown as 0s, and is updated based on your changes.

Both physical block view and logical block view are supported.

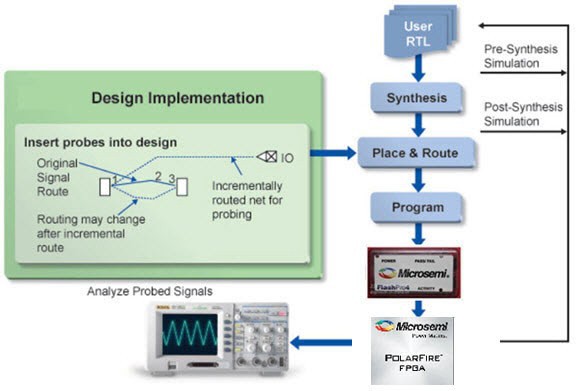

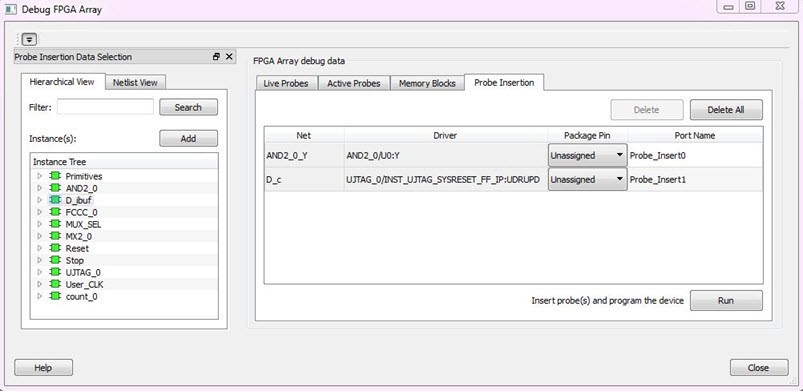

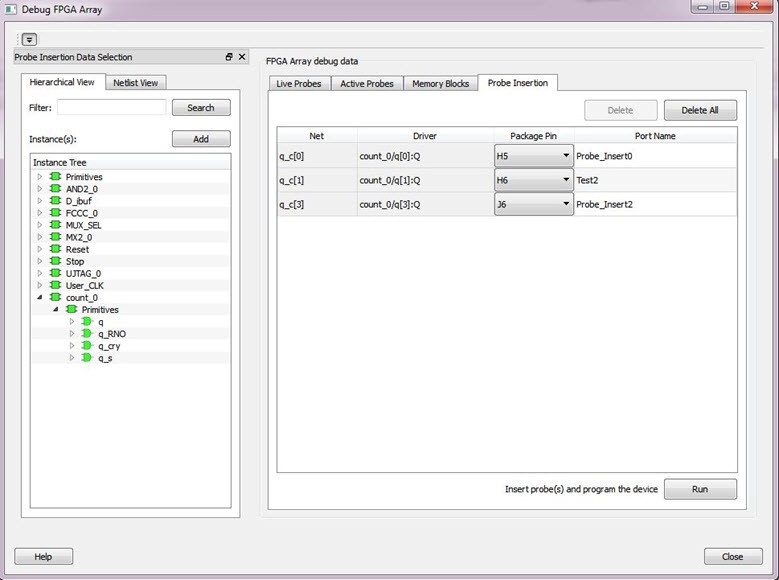

15.3.3.1.8 Probe Insertion (Post-Layout)

(Ask a Question)

The Probe Insertion debug feature is complementary to Live Probes and Active Probes. Live Probes and Active Probes use a special dedicated probe circuitry.

Inserting Probe and Programming the Device

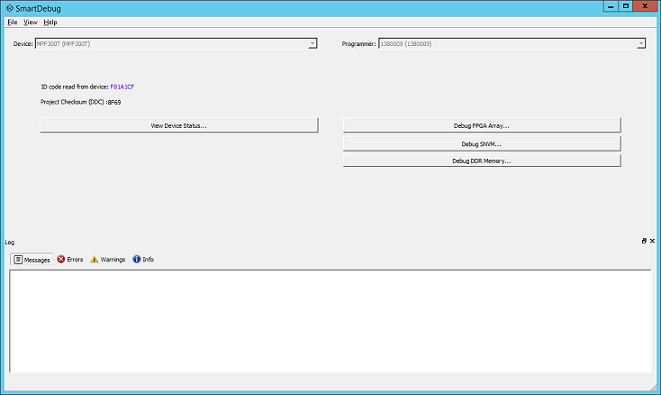

(Ask a Question)- Double click SmartDebug Design in the Design Flow window to open the SmartDebug window.Note: FlashPro Programmer must be connected for SmartDebug.

- Select Debug FPGA Array , and then select the Probe Insertion tab.

Figure 15-87. Probe Insertion Tab

In the left pane of the Probe Insertion tab, all available Probe Points are listed in instance level hierarchy in the Hierarchical view. All probe names are shown with the Name and Type in the Netlist View.

-

Select probe points from the Hierarchical View or Netlist View, right click and

choose Add to add them to the Active Probes UI. You can

also add the selected probe points by clicking the Add

button. The probes list can be filtered with the Filter

box.

Each entry has a Net and Driver name that identifies that probe point.

The selected net(s) appear in the Probes table in the Probe Insertion tab (see the following figure). SmartDebug automatically generates the Port Name for the probe. You can change the default Port Name if desired.

- Assign a package pin to the probe using the drop-down list in the Package Pin column. You can assign the probe to any unused package pin (spare I/O).

Figure 15-88. Debug FPGA Array > Probe Insertion > Add Probe

- Click Run.

This triggers Place and Route in incremental mode, and the selected probe nets are routed to the selected package pin. After incremental Place and Route, Libero automatically reprograms the device with the added probes.

The log window shows the status of the Probe Insertion run.

Deleting a Probe

(Ask a Question)Reverting to the Original Design

(Ask a Question)To revert to the original design after you have finished debugging:

- In SmartDebug, click Delete All to delete all probes.

- Click Run.

- Wait until the action has completed by monitoring the activity indicator (spinning blue circle). Action is completed when the activity indicator disappears.

- Close SmartDebug.

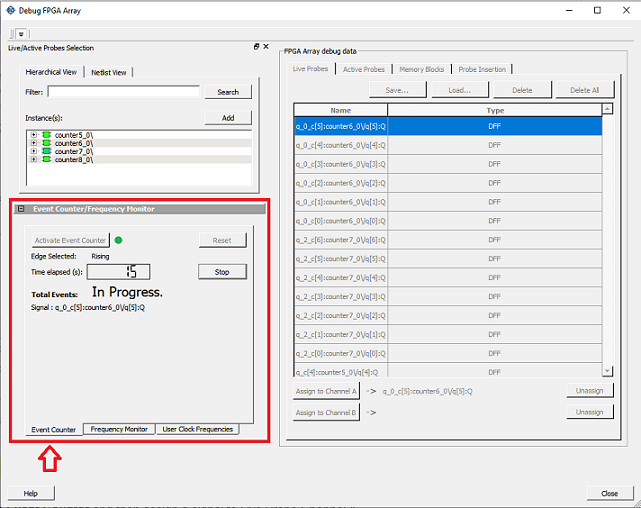

15.3.3.1.9 Event Counter

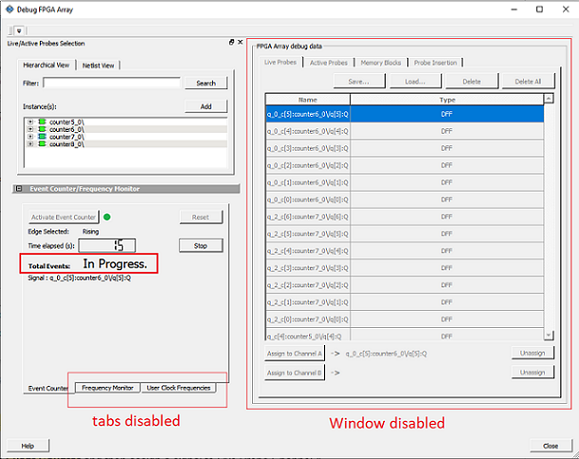

(Ask a Question)Enabling FPGA Hardware Breakpoint enables Event Counter in the SmartDebug tool (see section FPGA Hardware Breakpoint Auto Instantiation). This feature is used for any pseudo-static signal that does not toggle often. It counts the number of positive-edge transitions. Activate Event Counter is enabled when any signal or probe point from the selected list is assigned to Channel A via Live Probe. If you click Activate Event Counter, the count begins and the time elapsed is updated. Counting continues until the event counter is stopped using the Stop option. When Event counter is active, other tabs and features, such as Active Probes, Memory Blocks, and Probe Insertion are disabled.

Activating the Event Counter

(Ask a Question)To activate the Event Counter, assign a signal to Probe Channel A, and then click Activate Event Counter.

Running the Event Counter

(Ask a Question)When the Event Counter is active and in progress, a green LED appears next to the button as shown in the following figure. Time elapsed is shown in seconds. The Stop button is enabled to stop the counter. FPGA Array debug data and the control tabs in the Event Counter panel are disabled while running the Event Counter.

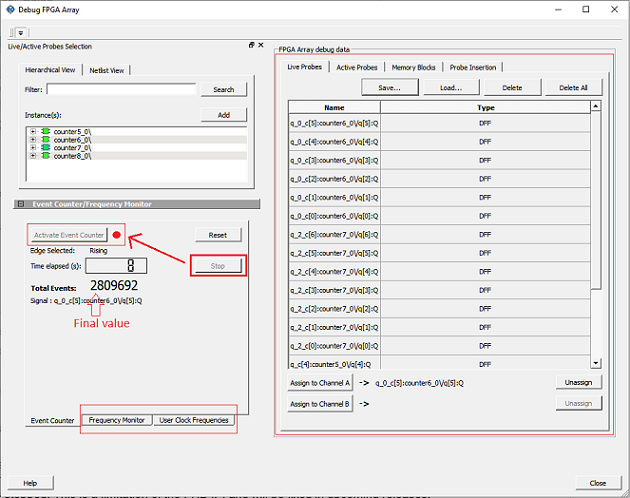

Stopping the Event Counter

(Ask a Question)To stop the Event Counter from counting, click the Stop button. A red LED appears when the Event Counter has stopped. FPGA Array debug data and the control tabs in the Event Counter panel are enabled when the Event Counter is not running.

For more information, see Frequency Monitor and User Clock Frequencies.

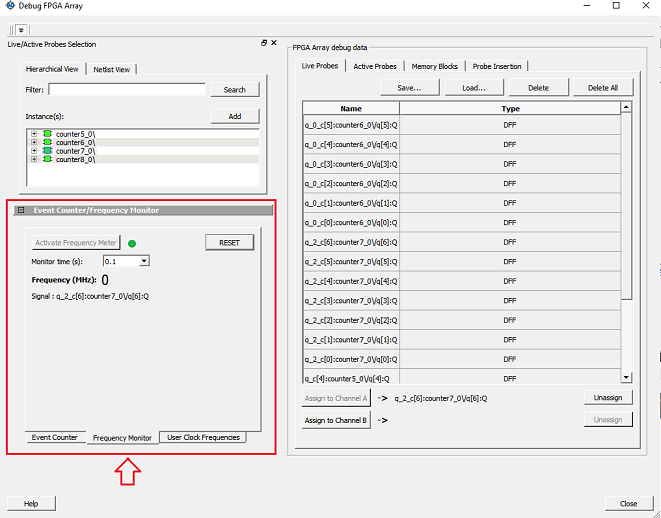

15.3.3.1.10 Frequency Monitor

(Ask a Question)Enabling FPGA Hardware Breakpoint enables Frequency Monitor in the SmartDebug tool (see section FPGA Hardware Breakpoint Auto Instantiation). The Frequency Monitor calculates the frequency of any signal in the design that can be assigned to Live Probe channel A. The Frequency Monitor is enabled when a probe point is assigned to Channel A via Live Probe.

The drop-down menu allows you to select the time to monitor the signal before the frequency is calculated. The accuracy of results increases as the monitor time increases. The unit of measurement is displayed in Megahertz (MHz). During the run, progress is displayed in the pane.

In the Frequency Monitor tab, you can activate the Frequency Monitor, change the monitor time (delay to calculate frequency), reset the monitor, and set the frequency in megahertz (MHz). Click the drop-down list to select monitor time value. During the frequency calculation, all tabs on the right side of the window are disabled, as well as the tabs in the FHB pane.

Activating the Frequency Monitor

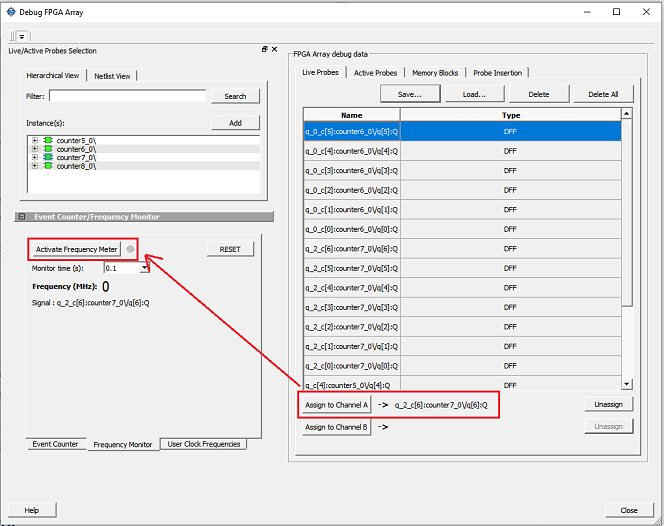

(Ask a Question)Assign a signal to Channel A, click the Live Probe tab, click the Frequency Monitor tab, and then click Activate Frequency Monitor.

-

Figure 15-94. Activating the Frequency Monitor

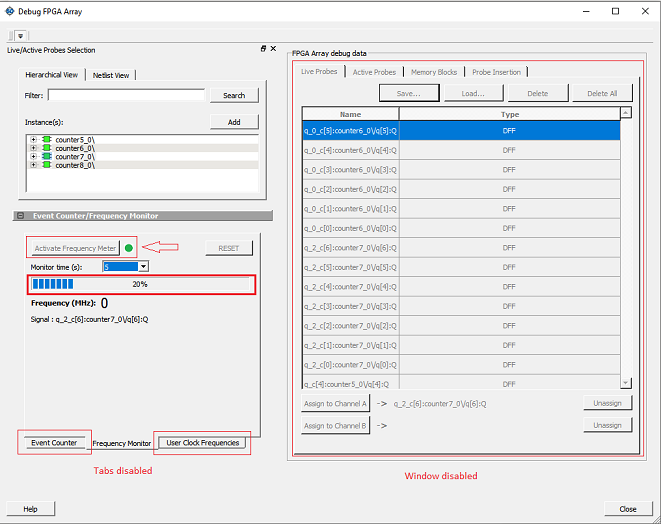

Running the Frequency Monitor

(Ask a Question)The Frequency Monitor runs automatically, and is indicated by a green LED. While it is running, FPGA Array debug data and the control tabs in the panel are disabled. A progress bar shows the monitor time progress when it is 1 second and above (see the following figure). The Reset button is also disabled during the run.

When a signal is assigned, the signal name appears next to Signal.

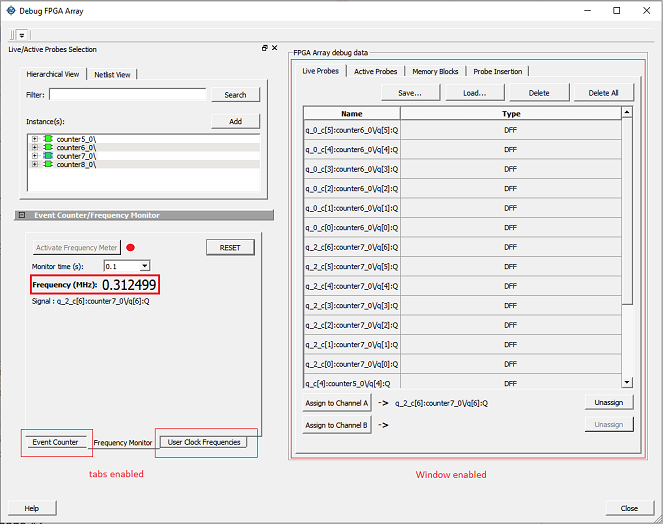

Stopping the Frequency Monitor

(Ask a Question)The Frequency Monitor stops when the specified monitor time elapses. This is indicated by a red LED. The result appears next to Frequency. The window and the tabs on the control panel are enabled. The Reset button is also enabled to reset the Frequency to 0 to start over the next iteration. The progress bar is hidden when the Frequency Monitor stops.

For more information, see Frequency Monitor and User Clock Frequencies.

15.3.3.1.11 FPGA Hardware Breakpoint Auto Instantiation

(Ask a Question)The FPGA Hardware Breakpoints (FHB) auto-instantiation feature automatically instantiates an FHB instance per clock domain that uses clocks (GL0, GL1, GL2, and GL3) from an FCCC instance. In PolarFire and PolarFire SoC, the instantiation is not limited to FCCC, it can be done on any of the four CLKINT types, such as CLKINT, GCLKINT, RCLKINT, and RGCLKINT. Enabling FHB auto-instantiation also enables the Event Counter and Frequency Monitor. The FHB instances gate the clock domain they are instantiated on. These instances can be used to force halt the design or halt the design through a live probe signal. After halting a selected clock domain or all clock domains, you can play or step on the clock domains. The FHB controls in the SmartDebug UI allow you to control the debugging cycle.

To enable this option:

- Launch Libero.

- Select . The Project settings dialog box appears.

- Select Design flow from the options available on the left pane of the dialog box.

- Select the Enable FPGA Hardware Breakpoints Auto Instantiation check box from the Root top options that appear on the right pane of the dialog box.

- In PolarFire and PolarFire SoC, you

must create an NDC constraints file in Constraint Manager and enter the following

command in the file to instantiate an FHB IP:

auto_instantiate_fhb -inst_name {<clkint name here>}. To instantiate FHB in all clock domains in the design, those many commands must be entered in the NDC file. This is auto-generated for other family devices.

- FHB auto-instantiation can also be done in the “Import netlist as VM file” flow.

- In PolarFire and PolarFire SoC, FHB can also be instantiated in the designs that have secured or encrypted components.

- The Spatial Debug Widget and FHB feature are hidden, and an INFO message is printed in the log if the user design has live probe I/Os enabled as input.

FHB Operations

(Ask a Question)If there is an auto-instantiated FHB instance in the design, FHB controls appear in the FPGA Operations tab.

Selecting a Clock Domain Mode

- If you select All Clock Domains , use the Halt

(Pause) , Play

, and Step

, and Step buttons to navigate through all clock domains.

buttons to navigate through all clock domains.

-

If you select Selected Clock Domain , select a clock domain from the Select Clock Domain drop-down. Use the Halt (Pause), Play, and Step buttons to navigate through the selected clock domain. If you switch clock domains, previous clock domain settings are not retained.

Specifying a Trigger

- If clock cycles are not required, click Arm Trigger to stop the DUT on the next positive edge that occurs on the signal connected to Live Probe PROBE_A.

- If clock cycles are required, enter a value between 0 and 255 for Delay Cycles Before Halt, and then click Arm Trigger. This setting configures the FHBs to trigger after the specified delay from the rising edge trigger. The delay is not applied to a forced Halt.

- The Trigger Signal appears as Not Connected until a live probe is assigned.

- When a probe is assigned to Live Probe PROBE_A, the Trigger Signal updates.

- Clicking Arm Trigger when a live probe connection is made disables FHB functions until the trigger is disarmed automatically or the design is force halted.

Live Probe Halt

To halt a selected clock domain or all clock domains (based on your clock mode selection), assign a signal to Live Probe PROBE_A in the Live Probes tab in the Debug FPGA Array dialog box, and then click the Active Probe tab to see the FPGA Hardware Breakpoint controls.

To arm the FHBs to look for a trigger on the signal connected to Live Probe PROBE_A, click Arm Trigger . After the trigger occurs, the clock domains are halted. If only one clock domain is halted, other clock domains continue to run, and you should anticipate results accordingly.

Actual delay cycles on hardware =

#Delay clock cycles before halt mentioned in smartdebug * (DUT clock frequency/FHB clock frequency)FHB clock frequencyFor more information, see Assumptions and Limitations.

Force Halt

To force halt a selected clock domain or all clock domains (based on your clock mode selection) without having to wait for a trigger from a live probe signal. Click the Halt button in the FPGA Hardware Breakpoint (FHB) controls.

- In the Operate on Selected Clock Domain mode, the state of the Halt button is updated based on the state of the clock domain selected.

- In the Operate on all Clock Domains mode, the Halt button is disabled only when all clock domains are halted. Each clock domain is halted sequentially in the order shown in the Select Clock Domain combo box.

Play Button

When the clock domain is in a halted state (live probe halt or force halt), clicking Play in the FPGA Hardware Breakpoint controls resumes the clock domain from the halted state.

In Operate on all Clock Domains mode, each clock domain runs sequentially in the order shown in Select Clock Domain.

Step Button

Once the clock domain is in a halted state (live probe halt or force halt), you can click the Step button in the FPGA Hardware Breakpoint controls. Clicking this button advances the clock domain by one clock cycle and holds the state of the clock domain. In All Clock Domains mode, each clock domain steps sequentially in the order shown in Select Clock Domain.

Waveform Capture

You can save the waveform view of the selected active probes using Export Waveform by specifying the number of clock cycles to capture in text box and then clicking Capture Waveform . The waveform is saved to a .vcd file.

To view the waveforms, import the .vcd file. You can then view the waveform file using a waveform viewer that supports the .vcd file format.

Trigger Input

To have an event in the DUT trigger the FHB IP (for example, a particular state in the FSM or counter value) when this signal is asserted, use the trigger input signal. If the trigger signal is already asserted (HIGH) when the FHB is armed, the DUT halts immediately.

Force Halt, Play, and Step operations are performed using the FHB controls. After the clock domain is halted, you can either force Play the clock domain or Step the clock domain by 1 clock cycle. To save the waveform view of the selected active probes, use Export Waveform by specifying the number of clock cycles to capture. The waveform is saved to a .vcd file.

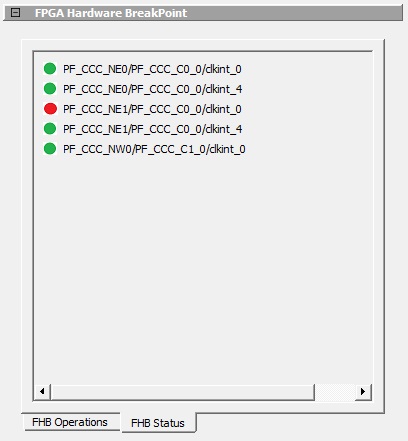

FHB Status

(Ask a Question)You can now view the status of all the FHB clock domains at the same time using the FHB Status tab on the FPGA Hardware Breakpoint widget. There is no Tcl command equivalent to this function.

The status of all FHB clocks in a sample design is shown in the following figure.

Assumptions and Limitations

(Ask a Question)- If you select the auto instantiation option in Libero and ran Synthesis, you must rerun Synthesis for the FHB-related functionality.

- In SmartFusion 2, IGLOO 2, and RTG4 devices, FHB is inserted on the Global clock outputs from CCC only.

- CLKINT_PRESERVE – FHB is not auto-instantiated if the user design contains this macro.

- In SmartFusion 2, IGLOO 2, and RTG4 devices, FHB instantiation is not supported in designs that have encrypted IP cores.

- EDIF using constraints flow is not supported.

- Live Probe triggering occurs on the Positive Edge only.

- In SmartFusion 2, IGLOO 2, and RTG4 devices, for imported verilog netlist files (.vm files), you must rerun synthesis to get FHB-related functionality. If synthesis is disabled and the netlist is compiled directly, FHB functionality is not inferred.

- If only one clock domain halts during operations, other clock domains continue to run, and you should anticipate results accordingly.

- FHB performance can only be

characterized against the clock which it is running at (that is, 160 MHz).

- If the DUT clock is running at or less than 160 MHz, the DUT clock halts within one clock cycle (1 or less).

- For frequencies higher than 160 MHz, the point at which the DUT halts cannot be ensured.

- FHB cannot be instantiated if a design has system controller Suspend Mode enabled.

- For all device families, FHB cannot be added to designs with System Controller Suspend Mode set to ON.

- For PolarFire and PolarFire SoC, the FHB auto-generates the FHB SDC file, obviating the need for you to create this file. However, the file does not appear in the Constraint Manager and is not available for you to manage. For other product families, the FHB SDC file is auto-generated and auto-associated by the FHB flow, and you can manage the SDC file through the Constraint Manager.

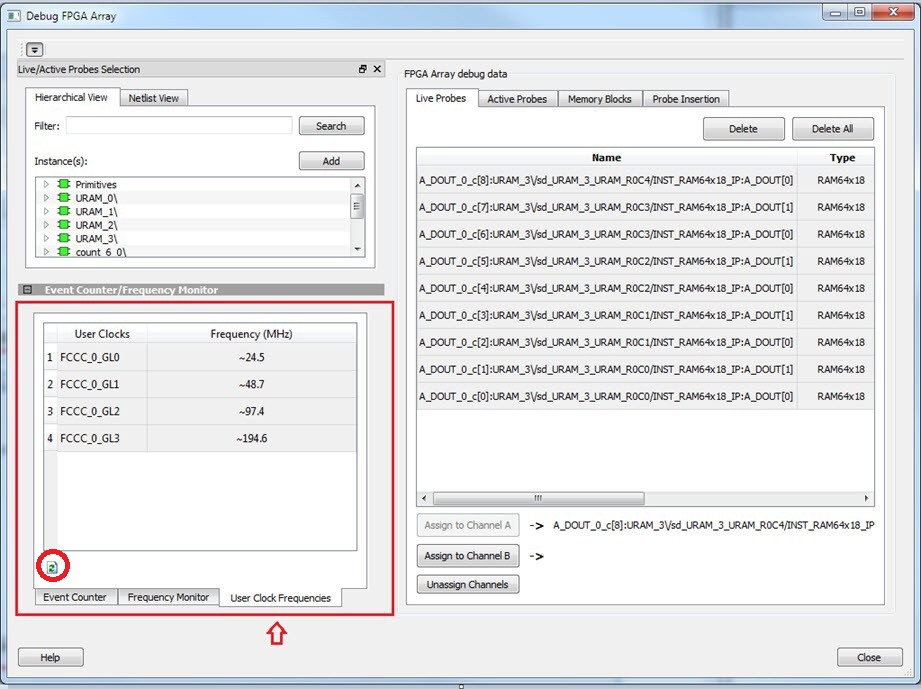

15.3.3.1.12 User Clock Frequencies

(Ask a Question)The User Clock Frequencies tab shows the frequencies that have been configured from the FCCC block. If assigned, live probe channels are temporarily unassigned, and reassigned after user clock frequencies have been calculated. The Refresh button (circled in the following figure) recalculates frequencies if clocks have been changed.

For related information, see Event Counter and Frequency Monitor.

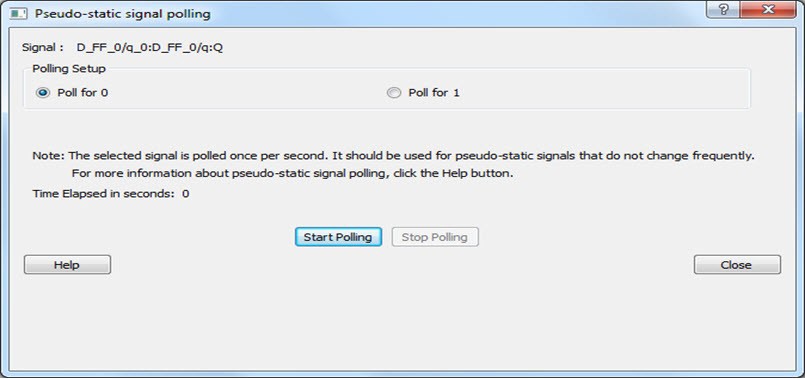

15.3.3.1.13 Pseudo Static Signal Polling

(Ask a Question)With Active Probes you can check the current state of any probe in the design. However, in most cases, you may not be able to time the active probe read to capture its intended value. For these cases, you can use Pseudo Static Signal Polling, in which the SmartDebug software polls the signal at intervals of one second to check if the probe has the intended value. This feature is useful in probing signals that reach the intended state and stay in that state.

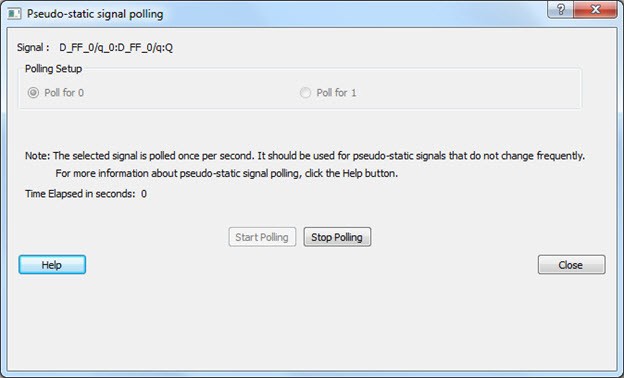

From the Active Probes tab in the Debug FPGA Array dialog box, right click a signal, bus, or group and select Poll to open the Pseudo-static signal polling dialog box as shown in the following figure.

Scalar Signal Polling

(Ask a Question)To poll scalar signals, select Poll for 0 or Poll for 1.

The selected signal is polled once per second. It should be used for pseudo-static signals that do not change frequently. The elapsed time is shown next to Time Elapsed in seconds.

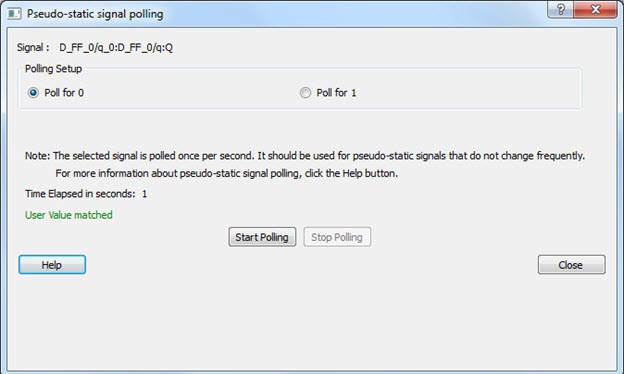

To begin polling, click Start Polling as shown in the following figure.

To end polling, click Stop Polling as shown in the following figure.

The elapsed time is updated in seconds until the polled value is found. When the polled value is found, User value matched is displayed in green in the dialog box as shown in the following figure.

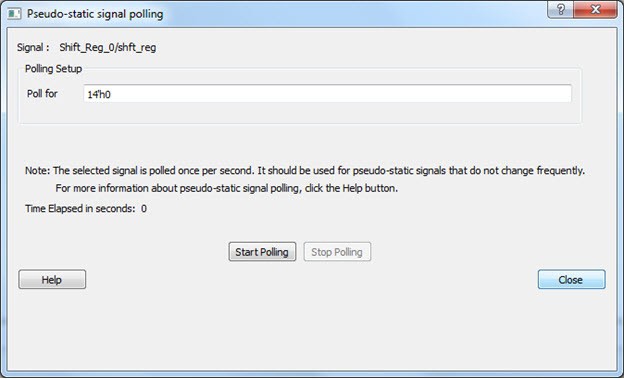

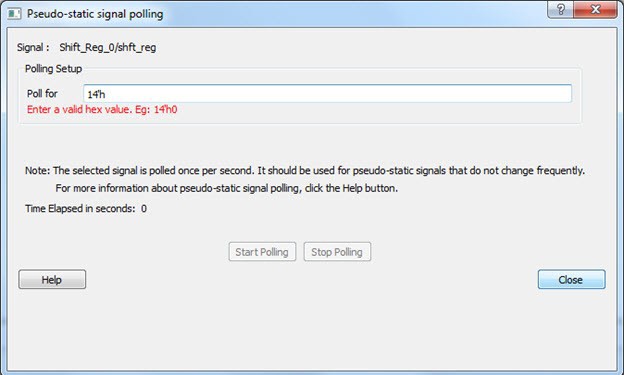

Vector Signal Polling

(Ask a Question)To poll vector signals, enter a value in the text box. The entered value is checked and validated. If an invalid value is entered, start polling is disabled and an example shows the required format.

When you enter a valid value and click Start Polling , polling begins.

To end polling, click Stop Polling.

The elapsed time is updated in seconds until the polled value is found. When the polled value is found, User value matched is displayed in green in the dialog box.

15.3.3.2 PolarFire and PolarFire SoC Debug Elements

(Ask a Question)The following sections describe the debug elements for PolarFire and PolarFire SoC.

15.3.3.2.1 Debug sNVM

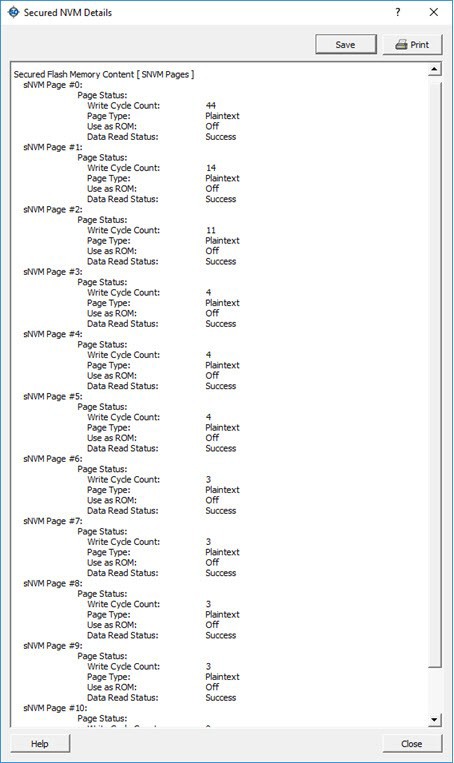

(Ask a Question)The sNVM block stores User data and UIC data. This data is stored as clients and can be configured in the Libero design. The USK (User Secret Key) security key secures pages within the memory. Authenticated data can be plain text or encrypted text, and non-authenticated data is plain text. SmartDebug helps the user read the page content of the sNVM block.

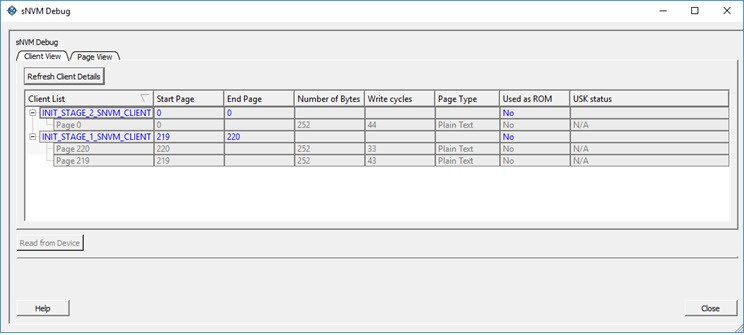

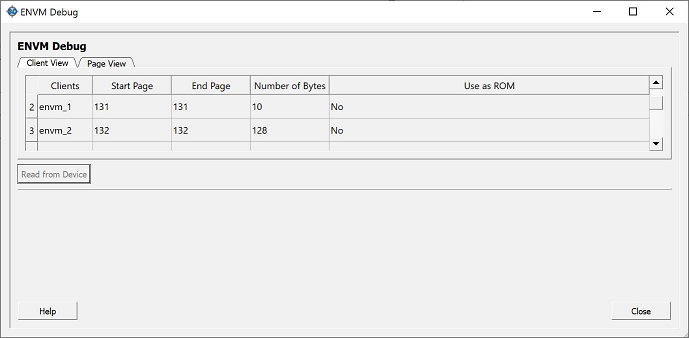

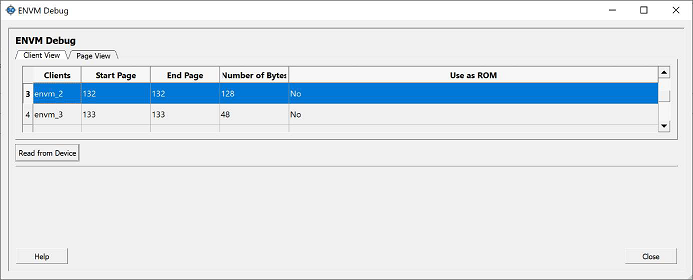

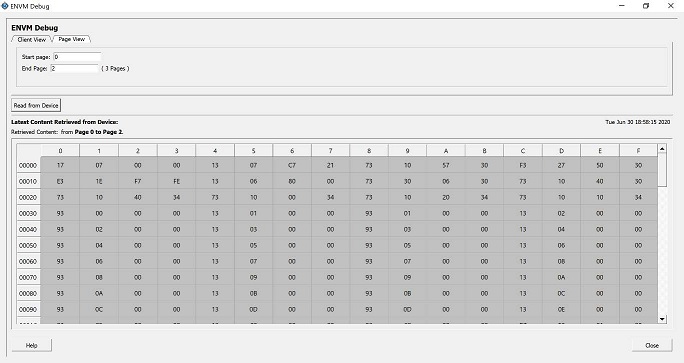

The sNVM Debug window has two tabs – Client View and Page View.

Client View

(Ask a Question)When the sNVM window opens, two tabs appear. Client information appears in the Client View tab when it is configured in the Libero design. Select a client to expand the table and see pages and page status inside the client. Click the Read From Device button to view the memory content.

You can select only one client at a time. Pages inside the client cannot be selected. The Start Page, End Page, and Number of Bytes are displayed for the selected client.

Click the View All Page Status button to see information for all pages in the client as shown in the following figure. Click the Export button to export the sNVM data to a text file.

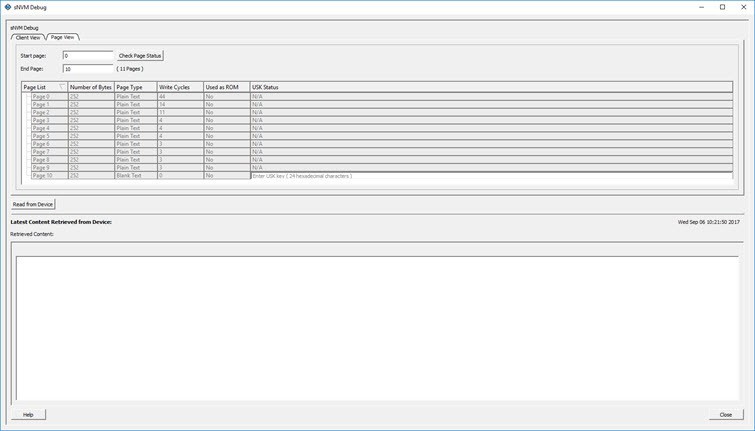

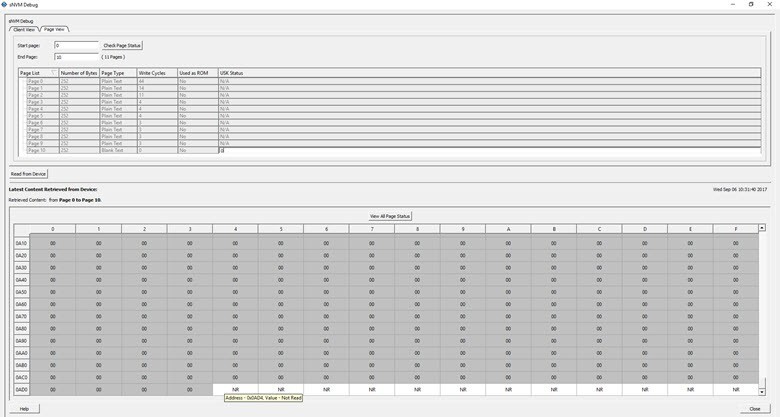

Page View

(Ask a Question)Page View is used to read a range of pages where start and end page have been specified.

If a page is secured, the default USK is used by SmartDebug to get the page status. If successful, the USK automatically reads the page. If a different USK has been set using system services, use the option to enter the USK, as shown in the following figure.

The following figure shows the specified page range.

The following figure shows the page status.

Read Operation

(Ask a Question)Client View

The Client View displays all the clients that are configured in the design. When a client is expanded, a table listing all pages is displayed.

When a client is selected, the Read from Device button is enabled. Click Read from Device to read the content of the client. A client can have one or more pages. Refresh Client Details option is given to the user to refresh the table. Click Refresh Client Details to update the information in SmartDebug and refresh the table. This is helpful when a client configuration is changed using system services.

Page View

Entering valid parameters and clicking Check Page Status displays a table of all pages with page status information. Pages in the table are read-only and cannot be selected. The page range included in Start Page and End Page is validated, and the Read from Device button is enabled. Click Read from Device to read the content.

Runtime Operations

(Ask a Question)After a design is programmed into the device, you can do the following:

- Change the content of a page.

- Authenticate a page.

- Change the security key of each configured page.

The preceding operations are not possible if the page is used as ROM. You can refresh page status in SmartDebug:

- Click the Refresh Client Details button in the Client View tab to refresh the client view table and update it with the latest changes.

- Click the Check Page Status button in the Page View tab to refresh the pages in the table.

If the security key has been changed, SmartDebug prompts you to enter the USK manually. Enter the USK in the USK Status column (Client View tab and Page View tab). By default, the USK entered in the configurator as the USK client is used to authenticate the page.

Demo Mode

(Ask a Question)Debug sNVM is supported in Demo Mode. The Client View and Page View are supported. Data from device initialization and configurators is shown in the Client View and User Design View.

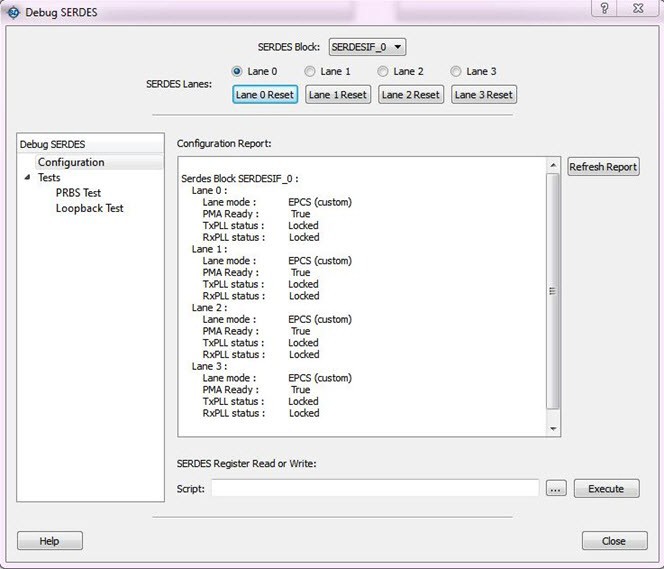

15.3.3.2.2 Debug Transceiver

(Ask a Question)The Debug Transceiver feature in SmartDebug checks the lane functionality and health for different settings of the lane parameters.

By default, lanes are configured in full duplex mode. Half duplex mode is also supported for each lane in the Quads. More information about half duplex mode lane configuration is provided in the following sections:

- Configuration Report

- SmartBERT

- Loopback Modes

- Static Pattern Transmit

- Eye Monitor

- Register Access

- Signal Integrity

- Optimize Receiver

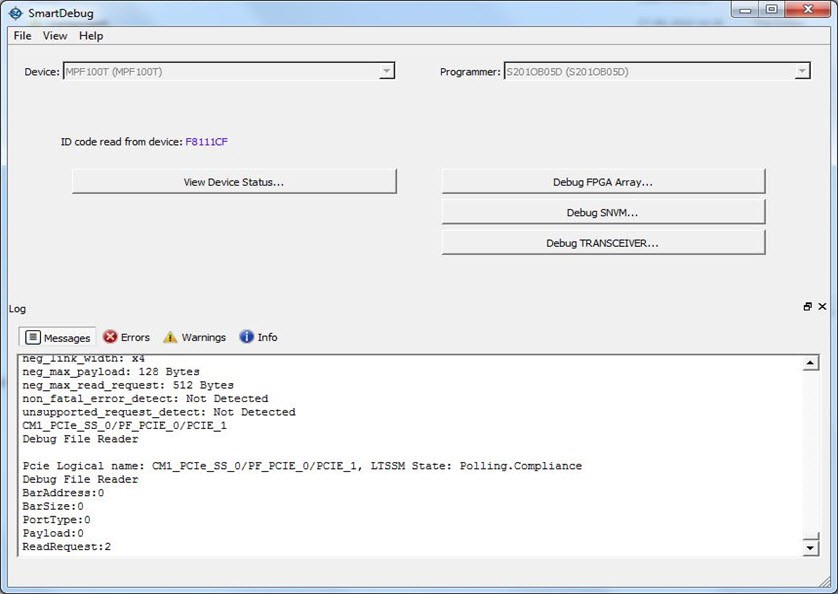

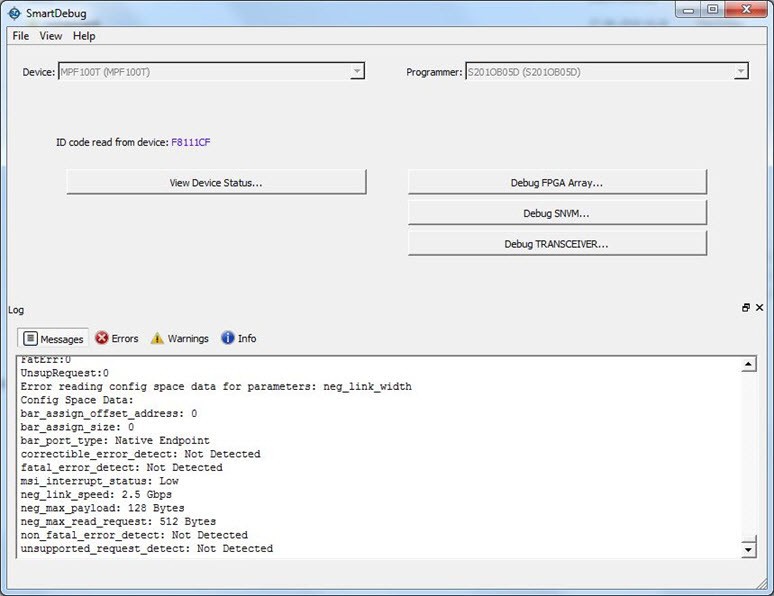

To access the Debug Transceiver feature in SmartDebug, click Debug Transceiver in the main SmartDebug window. This opens the Debug TRANSCEIVER dialog box.

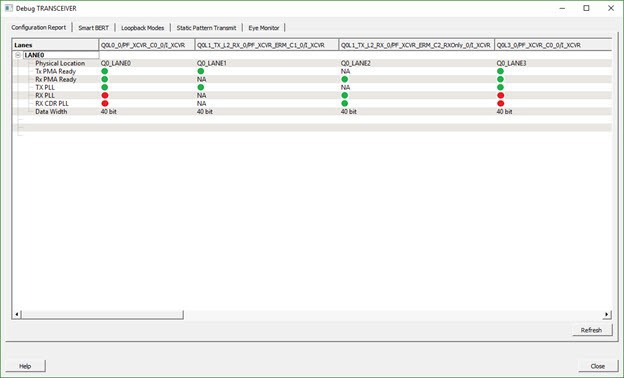

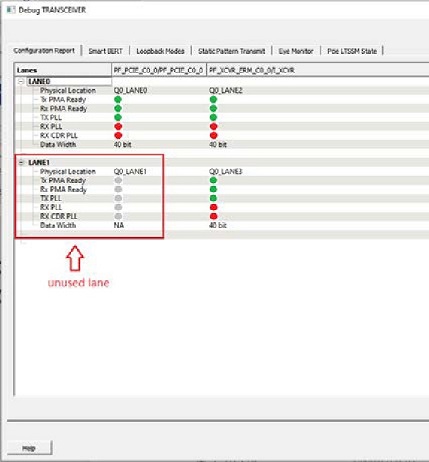

Configuration Report

(Ask a Question)Configuration Report is the first tab in the Debug TRANSCEIVER dialog box, and is shown by default when the dialog box opens. The Configuration Report shows the physical location, status/health, and data width for all lanes of all the quads enabled in the system controller.

Parameter information is shown in a tabular format, with lane numbers as rows and transceiver instance names as columns. The lane parameters are as follows:

- Physical Location: Physical block and lane location in the system controller.

- Tx PMA Ready: Indicates if the Tx of the lane is powered up and ready for transactions. Rx-only lane in half duplex mode is shown as "NA".

- Rx PMA Ready: Indicates if the Rx of the lane is powered up and ready for transactions. Tx-only lane in half duplex mode is shown as "NA".

- TX PLL: Indicates if the lane is locked onto TX PLL. Rx-only lane in half duplex mode is shown as "NA".

- RX PLL: Indicates if the lane is locked onto RX PLL. Tx-only lane in half duplex mode is shown as "NA".

- RX CDR PLL: Indicates if the lane is locked onto the incoming data. Tx-only lane in half duplex mode is shown as "NA".

Transceiver Hierarchy

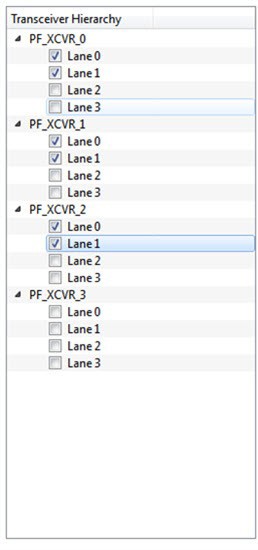

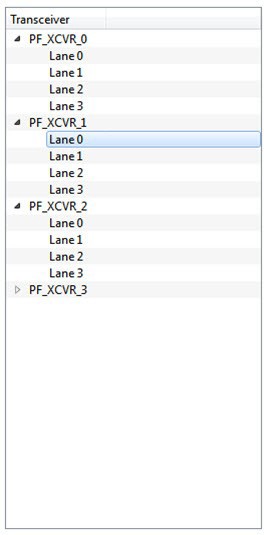

(Ask a Question)Transceiver Hierarchy view is a lane hierarchy with all the lanes instantiated in the design shown with respect to top level instance.

On the SmartBERT, Loopback Modes, and Static Pattern Transmit pages, check boxes allow multiple lanes to be selected for debug, as shown in the following figure.

On the Eye Monitor page, eye monitoring is done one lane at a time, as shown in the following figure.

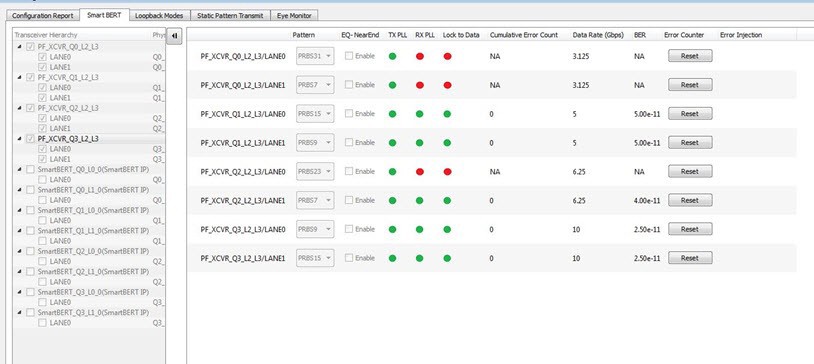

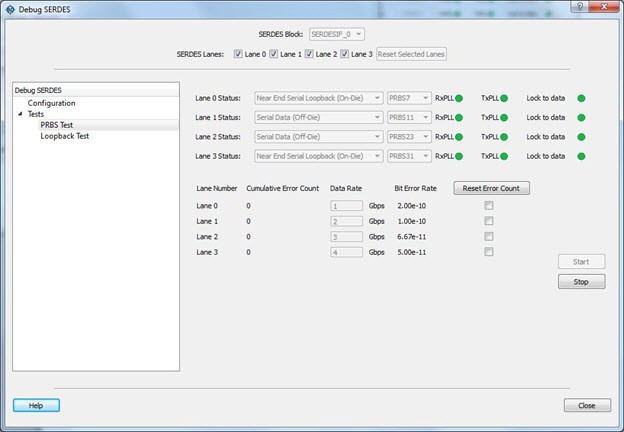

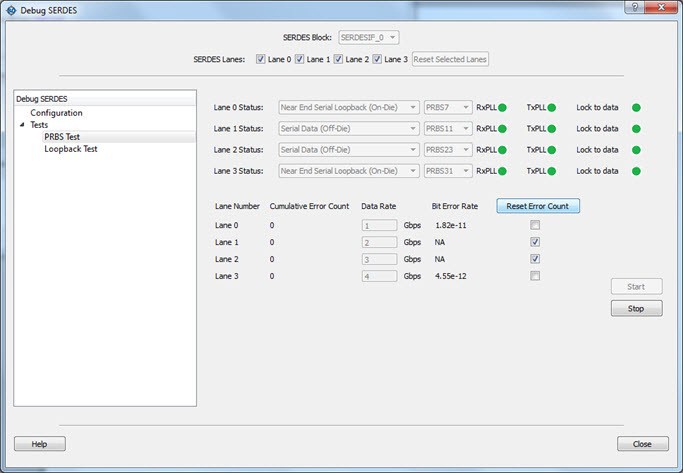

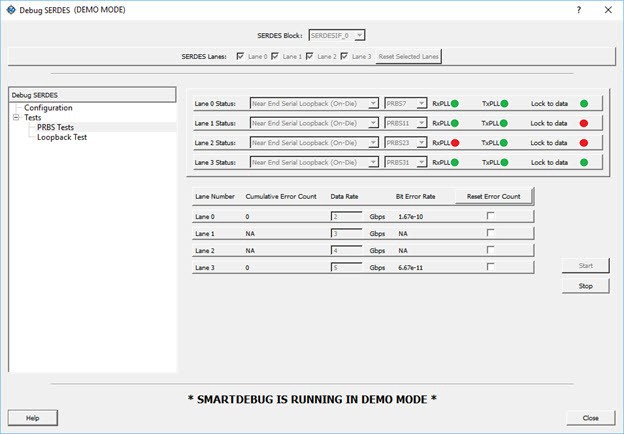

SmartBERT

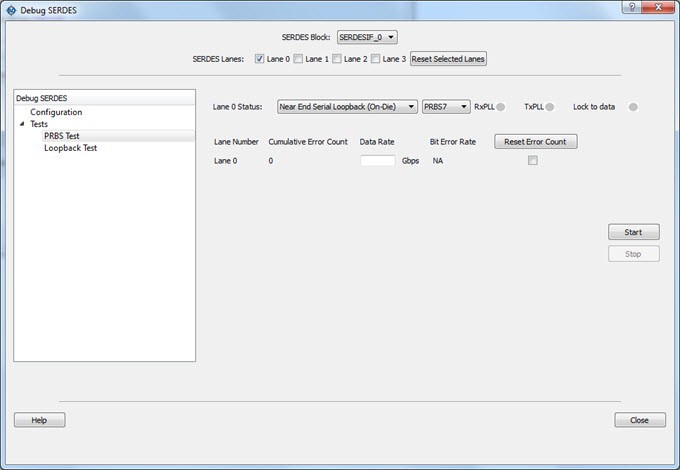

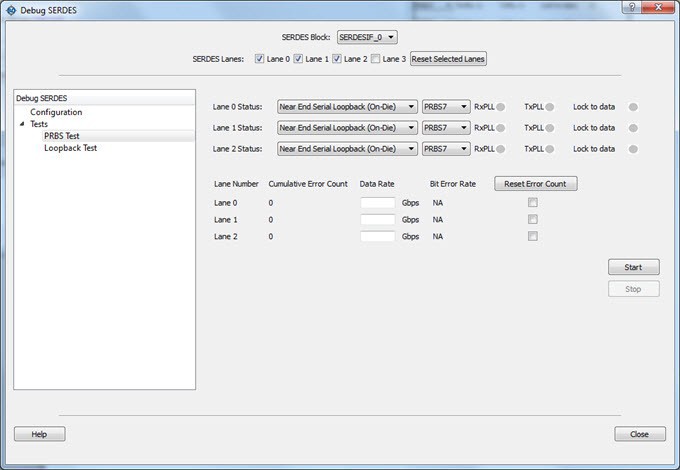

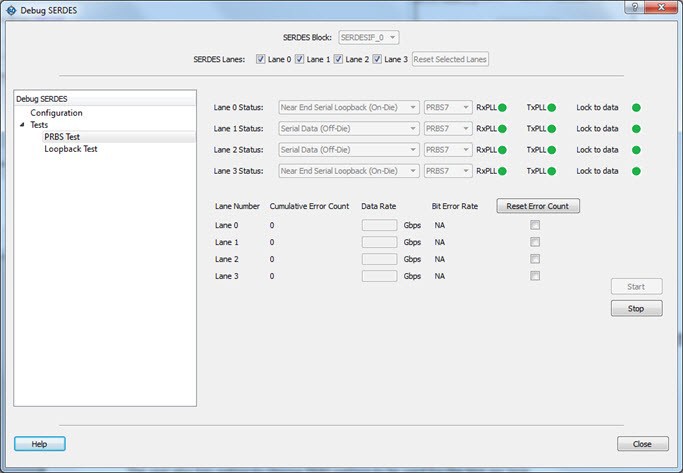

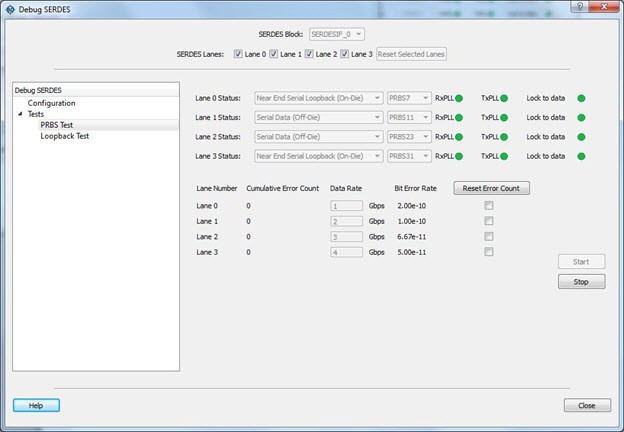

(Ask a Question)You can select lanes in the Transceiver Hierarchy and use debug options to run SmartBERT tests on the SmartBERT page of the Debug TRANSCEIVER dialog box.

Click the SmartBERT tab in the Debug TRANSCEIVER dialog box to open the SmartBERT page.

The following input options and outputs are represented as columns:

- Pattern: Input option. Select a PRBS pattern type from the drop-down list: PRBS7, PRBS9, PRBS15, PRBS23, or PRBS31. The default is PRBS7.

- EQ-NearEnd: Input option. When checked, enables EQ-NearEnd loopback from Lane Tx to Lane Rx. Disabled for half duplex mode.

- TX PLL: Indicates

whether a lane is locked onto TX PLL when the SmartBERT test is in progress. Rx Only lane in

half duplex mode is shown as "NA".

- Gray indicates test is not in progress.

- Green indicates lane is locked onto TX PLL.

- Red indicates lane is not locked onto TX PLL.

- RX PLL: Indicates if

lane is locked onto RX PLL when the SmartBERT test is in progress. Tx Only lane in half

duplex mode is shown as "NA".

- Gray: Indicates test is not in progress

- Green: Indicates lane is locked onto TX PLL

- Red: Indicates lane is not locked onto TX PLL

- Lock to Data:

Indicates if lane is locked onto incoming data / RX CDR PLL when the SmartBERT test is in

progress. Tx Only lane in half duplex mode is shown as "NA".

- Gray: Indicates test is not in progress

- Green: Indicates lane is locked onto TX PLL

- Red: Indicates lane is not locked onto TX PLL

- Cumulative Error Count: Displays the error count when the SmartBERT test is in progress.

- Data Rate: Data rates are shown according to the configured data rates for all duplex modes except for Independent TxRx, where both Tx data rate and Rx data rate are shown. See the preceding figure.

- BER: Calculates the Bit Error Rate (BER) from the cumulative error count and data rate and displays it in the column.

- Error Counter Reset: Resets the error counter and BER of the lane. A reset can be done at any time.

All output parameters are updated approximately once per second, with their values retrieved from the device. To add lanes, in the Transceiver Hierarchy, check the boxes next to the lanes to be added. To remove lanes, uncheck the boxes next to the lanes to be removed.

Select the desired options and click Start to start the Smart BERT test on all selected lanes. A popup message appears if a test cannot be started on one lane, multiple lanes, or all lanes. Tests will start normally on all unaffected lanes.

Click the Phy Reset button to do a Phy reset on all checked lanes in the Transceiver Hierarchy. This button is disabled when a PRBS test is in progress.

PCIe lanes x1 configuration exposes unused lanes that are disabled on all the tabs in the Debug TRANSCEIVER window.

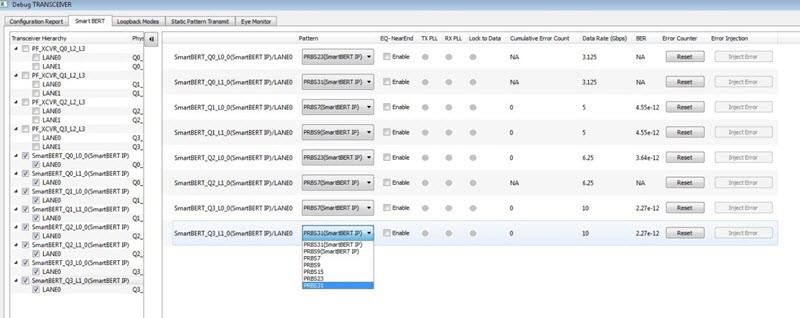

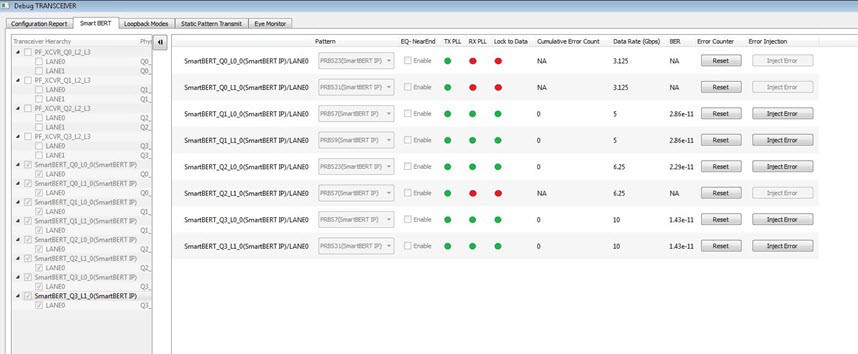

SmartBERT IP

(Ask a Question)The CoreSmartBERT core provides a broad-based evaluation and demonstration platform for PolarFire transceivers (PF_XCVR). Parameterizable to use different transceivers and clocking topologies, the SmartBERT core can also be customized to use different line rates and reference clock rates. Data pattern generators and checkers are included for each PF_XCVR, giving several different Pseudo-random binary sequences PRBS (27,223, 215 , and 231).

Each SmartBERT IP can have four lanes configured. Each Lane can have the pattern type PRBS7, PRBS9, PRBS23, or PRBS31 configured.

SmartDebug identifies the lanes that are used by the SmartBERT IP and distinguishes them by adding "_IP" to the SmartBERT IP instance name in the Transceiver Hierarchy.

You can expand a SmartBERT IP instance to see all the lanes. Check the check box next to a lane to add the lane to the SmartBERT IP page and include the lane in a PRBS test. If the box is unchecked, it will not be added as shown in the following figure.

You can select patterns for the added lane(s) from a drop-down list as shown in the following figure.

After the lane(s) have been added and the patterns(s) selected, click Start to enable the transmitter and receiver for the added lanes and patterns.

Error Injection

When SmartBERT IP lanes are added, you will see the Error Injection column and Error Inject button. Errors can be injected by clicking the Error Inject button when a PRBS test is running. This feature tests whether the error is identified by the pattern checker.

Error Count

Error Count is shown when a lane is added and a PRBS pattern is run. The error count can be cleared by clicking the Reset button under the Error Counter column.

The following figure shows the Reset and Inject Error buttons.

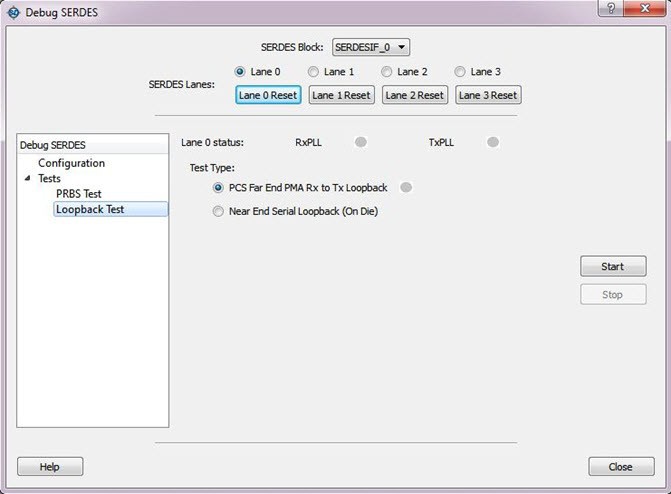

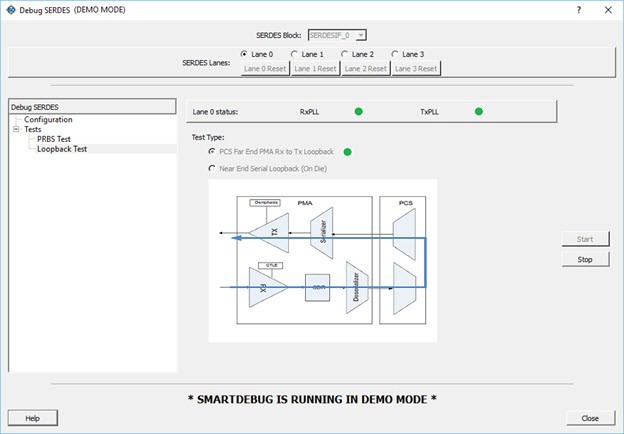

Loopback Modes

(Ask a Question)The Loopback Modes page in the Debug TRANSCEIVER dialog box allows you to select lanes from the Transceiver Hierarchy and use Loopback Mode debug options.

Click the Loopback Modes tab in the Debug TRANSCEIVER dialog box.

You can select the desired loopback type (EQ-NEAREND, EQ-FAREND, CDRFAREND, or No Loopback) for each lane.

- EQ-NEAR END: Set EQ-Near End loopback from Lane Tx to Lane Rx. This loopback mode is supported up to 10.3125 Gbps.

- EQ-FAR END: Set EQ-Far End loopback from Lane Tx to Lane Rx.

- CDR FAR END: Set CDR Far End loopback from Lane Rx to Lane Tx.

- No Loopback: Set this option to have no loopback between Lane Tx and Lane Rx. (For external loopback using PCB backplane or High Speed Loopback cables.)

Click Apply to enable the selected loopback mode on the lane(s).

Click Yes to ignore the changed selections and move to another selected page. Click No to remain on the current page.

Static Pattern Transmit

(Ask a Question)In the Static Pattern Transmit page of the Debug TRANSCEIVER dialog box, you can select lanes from the Transceiver Hierarchy and use Static Pattern Transmit debug options.

Click the Static Pattern Transmit tab in the Debug TRANSCEIVER dialog box to open the Static Pattern Transmit page.

When a lane is added from the Transceiver Hierarchy, the following debugging options can be selected:

- Pattern:

Pattern selection is available/enabled for all modes except Rx Only, because it is

applicable only for Tx. (and Tx is present in Full Duplex, Tx Only, and Independent

TxRx)

- Fixed Pattern is a 10101010... pattern. Length is equal to the data width of the Tx Lane.

- Max Run Length Pattern is a 1111000... pattern. Length is equal to the data width of the Tx Lane, with half 1s and half 0s.

- User Pattern is a user defined pattern in the value column. Length is equal to the data width.

- Value: Editor

available only with the User Pattern type. For other pattern type selections, it is

disabled.

- Takes the input pattern to transmit from the Lane Tx of selected lanes.

- Pattern type should be Hex numbers, and not larger than the data width selected.

- Internal validators dynamically check the pattern and indicate when an incorrect pattern is given as input.

- Mode: Currently, HEX mode is supported for pattern type.

- TX PLL:

Indicates Lane lock onto TX PLL when Static Pattern Transmit is in progress.

- Gray: Test is not in progress.

- Green: Lane is locked onto TXPLL.

- Red: Lane is not locked onto TXPLL.

- RX PLL :

Indicates Lane lock onto RX PLL when Static Pattern Transmit is in progress.

- Gray: Test is not in progress.

- Green: Lane is locked onto RXPLL.

- Red: Lane is not locked onto RXPLL.

Click Start to start the Static Pattern Transmit on selected lanes. Click Stop to stop the Static Pattern Transmit test on selected lanes.

Eye Monitor

(Ask a Question)You can determine signal integrity with the Eye Monitor feature. It allows you to create an eye diagram to measure signal quality. Eye Monitoring estimates the horizontal eye-opening at the receiver serial data sampling point and helps you select an optimum data sampling point at the receiver.

To use the Eye Monitor feature, perform the following:

- Start SmartDebug from Libero.

- Click the Eye Monitor tab in the Debug TRANSCEIVER dialog box.

Eye Scan Mode

(Ask a Question)Eye Monitor can be run in one of two modes: Normal mode or Infinite Persistent mode. Choose the desired mode in the Eye Scan Mode drop-down.

Normal Mode

(Ask a Question)In the Normal mode, Plot Eye performs single eye scanning and displays the Eye diagram as shown in the following example figure.

Infinite Persistent Mode

(Ask a Question)- This feature is not available for Tx Only mode

- Eye plot is disabled for lanes with a data-rate less than 3 Gbps

The Start Plot Eye button changes to Stop Plot Eye and the infinite scanning and cumulation process begins. In every iteration, the eye is cumulated with all previous eyes to make a single “cumulative eye”. This cumulative eye appears with a color scheme in the GUI, as shown in the following figure. The completed iteration number, and the cumulative BER is updated and appears after every iteration, along with the cumulative eye. To stop cumulative eye monitoring, click Stop Plot Eye. The process halts after the current iteration completes.

Clear

(Ask a Question)Additional Eye Output Text Files

(Ask a Question)Data files are generated in Normal mode and Infinite Persistent mode. These files contain the eye data errors in the matrix format. The name of the file is Plot_Eye*.txt, where * stands for numbering starting from 1.

The files are generated in the designer folder of the Libero project for integrated SmartDebug from Libero and in the standalone project folder for the standalone SmartDebug.

- In the Normal mode, one eye data error file is generated, as eye scanning is done only once.

- In Infinite Persistent mode, one file is generated per iteration.

Ensure to have sufficient space in the project location when running Infinite Persistent eye monitoring. The numbering used in the file naming continues to increment until the infinite persistent mode eye plot activity is in progress.

Error Handling

(Ask a Question)Eye Scanning can be performed successfully only if there is data traffic on the Lane Rx when Eye Monitoring is in progress. In Normal Mode, when an Eye Scan fails, a popup message is displayed. In Infinite Persistent mode, when an Eye Scan fails in any iteration, a popup message is displayed and Eye scanning terminates.

Eye Mask

(Ask a Question)The Eye mask feature has been added to both the normal and infinite persistent modes in the Libero SoC v12.5 release. Eye mask provides a guide to where the best eye opening with least errors can be seen. Both the Apply Mask and the Clear Mask buttons are disabled in the Default View. Click Plot Eye to enable the Apply Mask button.

After applying the mask, the Clear Mask button is enabled and the Eye Mask for the Eye Plot appears.

Click Clear Mask to clear the Eye Mask for the current Eye Plot and enable the Apply Mask button.

Design Initiated Eye Plots

(Ask a Question)After you run Eye Monitor in an embedded application such as IAR Embedded Workbench using the PolarFire Transceiver driver, you can display the associated eye plots. When the eye monitor firmware is run, the terminal log is stored in a text file located in the root folder. This file is compatible with SmartDebug to view the eye plots.

- Select Eye Scan Mode Design Initiated Eye Plot. The Browse option becomes enabled.

- Select the eye plot log files from the dialog box. The Select Eye Output drop-down menu is enabled.

- In the Select Eye Output drop-down menu, select a plot by its tag-name. The Plot Eye option is enabled.

- Click Plot Eye. The eye diagram loads on the canvas.

To start eye monitoring for the lane, select Eye output from the Select Eye Output drop-down, and click Plot Eye . The Eye diagram appears, as shown in the following figure.

Power On/Off Eye Monitor

(Ask a Question)Switching Off Power to the Eye Monitor Core

(Ask a Question)To save power, switch off the power to the eye monitor core.

The default option is provided after reading the status from the device. To power off the eye monitor, click Power Off Eye Monitor (the button toggles to Power on Eye Monitor). Clicking the button again powers on the eye monitor.

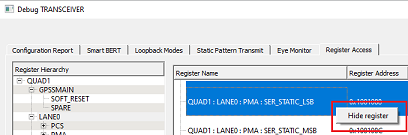

Register Access

(Ask a Question)The Register Access page in the Debug TRANSCEIVER window allows you to perform register read, write, export, hide, and export all register operations. The list at the top of the page allows you to show all registers or show only the registers whose read value has been changed. By default, Show All Registers is selected. The exported register details are saved in a .csv file.

The following table describes the various interface elements on the page.

| Option | Description |

|---|---|

| Register Hierarchy | Lists the design specific registers in a collapsible tree view format. |

| Register Name | Displays the name of the register that can be looked up in the Register Hierarchy. |

| Register Address | Displays the physical address of a register. The address is shown in hexadecimal format. The address is calculated based on the Quad, lane number, register type, and offset. |

| Access Type | Specifies the register access type. This column also indicates the field access types when a register is expanded. |

| Field Name | Displays the field name based on the register information read from the PF_XCVR.xml file. |

| Field Bits | Displays bit value based on the field offset and the width of the register. |

| Prev Read Value | Displays the previously read value. By default, unread is displayed. |

| Curr Read Value | Displays a register's current value. |

| Read Value | Displays the value read from the device. Click the Read button to retrieve the value from the device. By default, unread is displayed. |

| Write Value (Hexadecimal) | Enter a hexadecimal register value. |

| Import | Click to load the registers from a .csv file that is

exported. This option loads the register list in the selected pane. Any

registers selected earlier will be prompted to delete or cancel the load

operation. |

| Delete All | Click to delete all selected registers. |

| Read | Click to retrieve the register value from the device. Note: The

Read button is disabled when no register

is selected in the Register Hierarchy tree

view or when SmartDebug is running in the Demo mode. |

| Write | Click to write the user specified register value. Note: The

Write button is disabled when no value is

specified in the Write Value(Hexadecimal)

text box of the selected register or when SmartDebug is running in

the Demo mode. |

| Export | Click to save the selected register details to a

.csv file. When clicked, the

Register Access Export Action dialog box

appears. Specify the file name and the location of the file in the

dialog box. Note: The Export button is disabled

when SmartDebug is running in the Demo mode. |

| Export All | Click to save all the register details to a .csv

file. When clicked, the Register Access Export All

Action dialog box appears. Specify the file name and the

location of the file in the dialog box. The exported .csv file contains the register name, address, field name, field bits, read, and write values of registers. The first row of the file contains the header information. Register values are written from the second row onwards. |

| Hide register | Select register(s) and right click to view this option. The

Hide registers context menu option helps you

remove the selected register(s) from the Register

Access table. |

Signal Integrity

(Ask a Question)The Signal Integrity feature in SmartDebug works with Signal Integrity in the I/O Editor, allowing the import and export of .pdc files.

The Signal Integrity pane appears in the following SmartDebug pages:

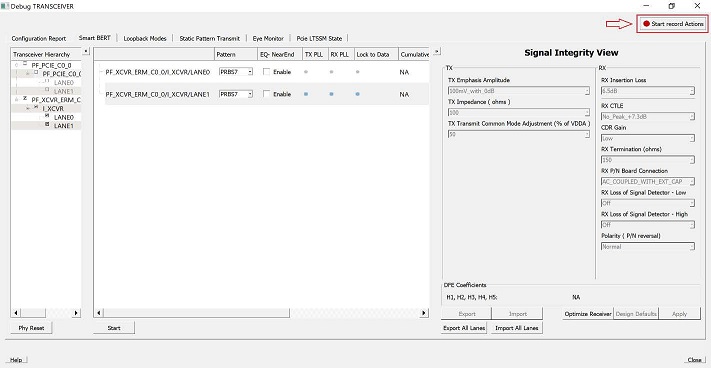

When you open Debug Transceiver in SmartDebug and click the SmartBERT, Loopback Modes, Static Pattern Transmit, or Eye Monitor tab, all parameters in the Signal Integrity pane are shown as Undefined. Only the Export All Lanes and Import All Lanes buttons are enabled. See the following figure.

In full duplex mode, all parameters (Tx and Rx) are imported/exported.

The following figure shows Signal Integrity for Tx Only mode, Rx Only mode, and Independent TxRx mode.

The following figure shows Signal Integrity for Rx Only mode. In this mode, only Rx parameters are imported and exported.

The following figure shows Signal Integrity for independent TxRx mode. In this mode, Tx and Rx parameters are imported and exported.

When a lane is selected in the SmartBERT, Loopback Modes, Static Pattern Transmit, or Eye Monitor pages, the corresponding Signal Integrity parameters (configured in the I/O Editor or changed in SmartDebug) are enabled and shown in the Signal Integrity pane.

The selected lane instance name is displayed in the Signal Integrity group box, and the Export, Import, and Design Defaults buttons are enabled.

You can select options for each parameter from the drop-down for that parameter. Click Apply to set the selected transceiver instance with the selected options.

The Polarity (P/N reversal) parameter has been added. You can choose

Normal or Inverted from the drop-down

menu. This parameter is not available for MPF300T_ES (Rev C) or MPF300T_XT (Rev E)

devices.

The CDR Gain parameter has been added for MPF300T, MPF100T, MPF200T, MPF500T

devices, and you can select the High or Low option from the drop-down. This parameter is

supported for Export, Export All, Import, Import All, Design Defaults, and Apply flows

of Signal Integrity. This parameter is not available for MPF300T_ES (Rev C) or

MPF300T_XT (Rev E) devices.

If you change parameter options Tcl and click another lane, move to another tab, or click Import, Import All, or Design Defaults without applying the changes, the following message appears: Some Signal Integrity options are modified. How do you wish to continue?

Click Apply to apply the changes or Discard to discard the changes.

To ensure that the Signal Integrity in SmartDebug is in sync with the Signal Integrity state of the device, click the Design Defaults button in SmartDebug. This sets the SI in the Signal Integrity tab to the design constraints (SI parameter values chosen from the I/O Editor).

Design Defaults

(Ask a Question)Clicking the Design Defaults button loads the Signal Integrity parameter options for the selected lane instance. These are the signal integrity settings that were selected in the Libero design flow run and reside in the STPL file. Design Default parameter options are applied to the device.

Export

(Ask a Question)Clicking the Export button exports the current selected parameter options and other physical information for the selected lane instance to an external PDC file. A pop-up box prompts you to choose the location where you want the .pdc file to be exported.

The exported content will be in the form of two set_io commands, one for the TXP port and one for the RXP port of the selected lane instance.

Export All Lanes

(Ask a Question)Clicking the Export All Lanes button exports the current selected parameter options and other physical information for all lane instances in the design to an external PDC file. A pop-up box prompts you to choose the location where you want the .pdc file to be exported.

Import

(Ask a Question)Clicking the Import button imports Signal Integrity parameter options and other physical information for the selected lane from an external PDC file.

The Signal Integrity parameter options are applied to the device and updated in Modified Constraints.

Import All Lanes

(Ask a Question)Clicking the Import All Lanes button imports Signal Integrity parameter options and other physical information for all lanes from an external PDC file.

The Signal Integrity parameter options are applied to the device and updated in Modified Constraints.

Signal Integrity and Calibration Report

(Ask a Question)You can generate and extract an additional report containing Signal Integrity parameters and options, CTLE register settings, and DFE coefficients by clicking Export or Export all in SmartDebug. Click Export to export the report only for the selected lane. Click Export all to export a report for all the lanes. This report is a text file that contains the Signal Integrity parameters and options, CTLE register values {CST1, RST1, CST2, RST2}, and DFE coefficient values {H1, H2, H3, H4, H5}. The exported file has a .txt extension with the same name as the .pdc file, and is exported in the same location. DFE Coefficients are exported only for DFE configured lanes. See the following report.

SIGNAL INTEGRITY AND CALIBRATION REPORT

=========================================================================== PF_XCVR_3/LANE0

Signal Integrity:

TX_EMPHASIS_AMPLITUDE=400mV_with_-3.5dB

TX_IMPEDANCE=150 TX_TRANSMIT_COMMON_MODE_ADJUSTMENT=50

TX_POLARITY=Normal

TXPLL_BANDWIDTH=LOW

RX_INSERTION_LOSS=6.5dB

RX_CTLE=3GHz_+5.5dB_2.1dB

RX_TERMINATION=100

RX_PN_BOARD_CONNECTION=AC_COUPLED_WITH_EXT_CAP

RX_LOSS_OF_SIGNAL_DETECTOR_LOW=PCIE

RX_LOSS_OF_SIGNAL_DETECTOR_HIGH=PCIE

RX_POLARITY=Normal

-

CTLE Coefficients:

CST1, RST1, CST2, RST2 = 3, 3, 1, 2

-

DFE Coefficients:

H1, H2, H3, H4, H5 = 0, -1, 2, 6, 3

===================================================================================

PF_XCVR_3/LANE0

Signal Integrity:

TX_EMPHASIS_AMPLITUDE=400mV_with_-3.5dB

TX_IMPEDANCE=100

TX_TRANSMIT_COMMON_MODE_ADJUSTMENT=80

TX_POLARITY=Normal

TXPLL_BANDWIDTH=LOW

RX_INSERTION_LOSS=17.0dB

RX_CTLE=3GHz_+5.5dB_2.1dB

RX_TERMINATION=100

RX_PN_BOARD_CONNECTION=AC_COUPLED_WITH_EXT_CAP

RX_LOSS_OF_SIGNAL_DETECTOR_LOW=PCIE

RX_LOSS_OF_SIGNAL_DETECTOR_HIGH=PCIE

RX_POLARITY=Normal

-

CTLE Coefficients:

CST1, RST1, CST2, RST2 = 3, 1, 2, 2

-

DFE Coefficients:

H1, H2, H3, H4, H5 = Not applicable for CDR configured laneSignal Integrity Parameters in Half Duplex Modes

(Ask a Question)Tx Only XCVR Mode

- The Signal Integrity view shows only Tx parameters.

- Lane information is also shown in the Signal Integrity view.

- Optimize Receiver is disabled.

- The Export option exports only Tx parameters.

- The Import option imports only Tx parameters. If Rx parameters are present, the tool errors out.

Rx Only XCVR Mode

- The Signal Integrity view shows only Rx parameters.

- Lane information is also shown in the Signal Integrity view as a header.

- Optimize Receiver is enabled.

- The Export option exports only Rx parameters.

- The Import option imports only Rx parameters. If Tx parameters are present, the tool errors out.

Independent TxRx XCVR Mode

This mode is displayed as full duplex mode (no changes).

Optimize Receiver

(Ask a Question)The Optimize Receiver function allows you to optimize the DFE coefficients and/or CTLE settings for the selected lanes, depending on receiver mode. For CDR mode receivers, CTLE settings and/or DFE coefficients can be optimized. For DFE mode receivers, CTLE settings and DFE coefficients can be optimized.

For DFE coefficients, the optimize function runs through an algorithm for each lane and sets the best available coefficients for each selected lane for the current temperature, voltage, and data pattern conditions. After the optimization is complete, the transceiver lanes are set to these coefficients for the user to continue debugging.

For information about how to use the optimized coefficients without SmartDebug, see the PolarFire Family Transceiver User Guide

Click Optimize Receiver to open the Optimize Receiver dialog box. Full duplex, Rx Only, and Independent TxRx are shown (Tx Only lanes are not shown).

Display DFE Coefficient Values

(Ask a Question)The DFE coefficients H1, H2, H3, H4, and H5 are displayed as non-editable in the Signal Integrity pane for any lane configured in the DFE or CDR mode. See the following figure.

- DFE coefficients are shown for CDR mode receivers if force DFE calibration is selected. This can be done from the check box provided inside the Optimize Receiver dialog box (shown in section Optimize Receiver).

- The DFE coefficients are read from the register fields as follows:

H1 = H1_MON H2 = H2_MON H3 = H3_MON H4 = H4_MON H5 = H5_MON - DFE coefficients are read back from the device in the following scenarios:

- When the lane is selected in the SmartBert, Loopback Modes, Static Pattern Transmit, and Eye Monitor pages.

- When a test is started/stopped on selected lane in the SmartBert page.

- When a test is started/stopped on selected lane in the Static Pattern Transmit page.

- When Optimize Receiver is executed on the selected lane.

Exporting DFE Coefficients

(Ask a Question)Optimized DFE coefficient values are saved in a *.txt file when you click

Export. The text file is saved in the same location where the

physical design constraint (*.pdc) file is saved when the

Export or Export All operation is

performed.

During the export process, a Physical Design Constraints (*.pdc) file is

generated, which includes the set_io command along with the DFE Coefficient

parameters such as RX_DFE_COEFFICIENT_H1.

*.txt file) to the *.pdc file, ensuring they are arranged

in the correct sequence, from H1 to H5.PCIE Debug

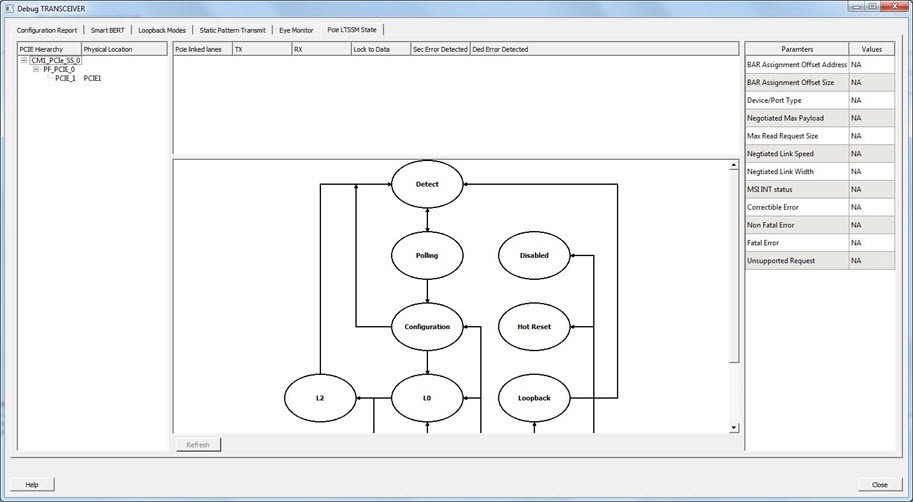

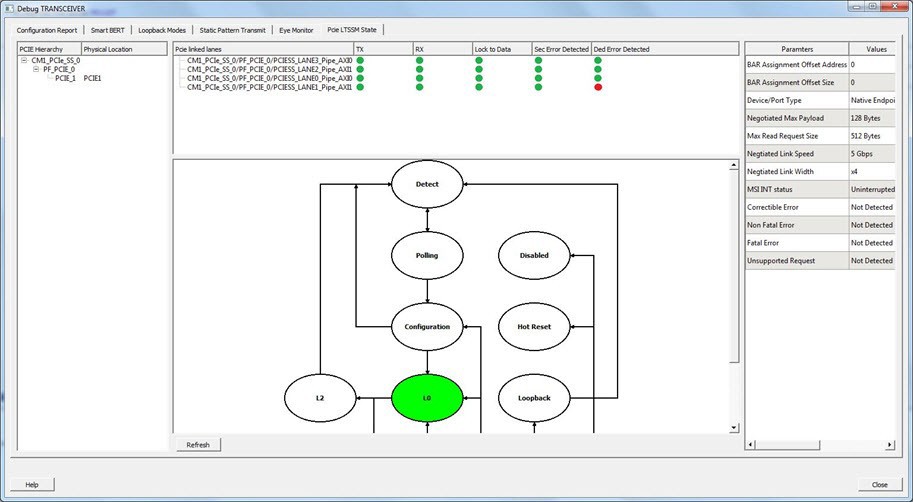

(Ask a Question)The PCIE LTSSM State page is available in Debug TRANSCEIVER when PCIE has been instantiated in a design.

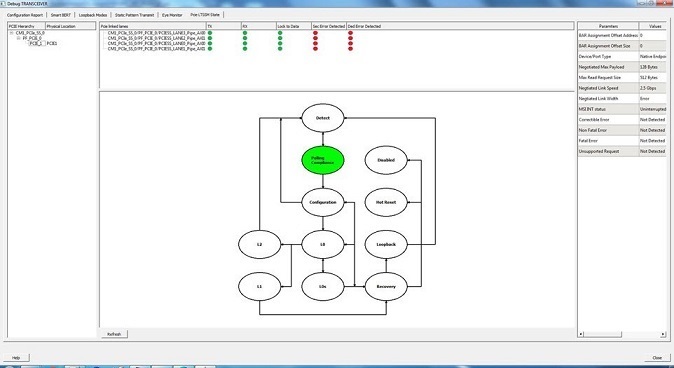

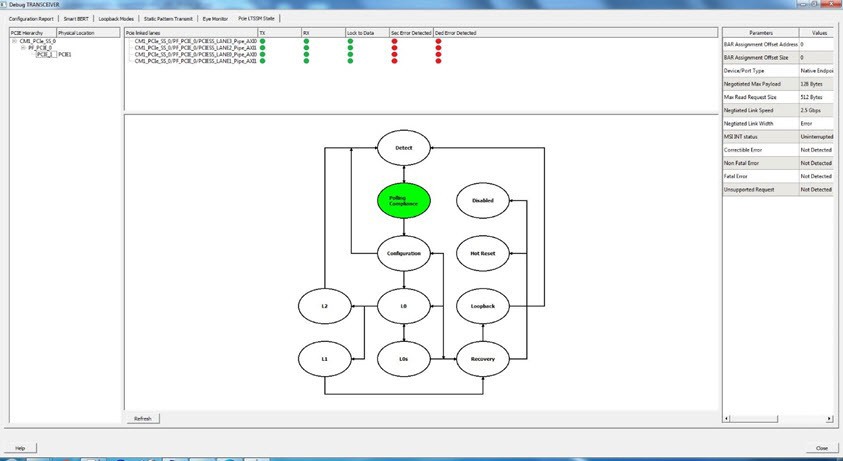

The PCIE LTSSM State page shows the PCIE Design Hierarchy. It contains the tree hierarchy of the PCIE instance in the design, as shown in the following figure. The physical location of the PCIE instance is shown beside the PCIE instance in second column.

Lane Status and Lane Link Error Status

(Ask a Question)When a PCIE instance is selected (without selecting any other hierarchy level above), the Lane status, SEC Error status, and DED Error status is shown to the right of the PCIE Hierarchy. The logical names of the lanes are also shown. See the following figure.

LTSSM State Machine

(Ask a Question)The PCIE LTSSM State page shows the LTSSM state machine to the right of PCIE Design Hierarchy and under the lane status, as shown in the following figure.

When you click a PCIE instance in the PCIE Hierarchy, the active LTSSM state is retrieved from register LTSSM_STATE:PL_LTSSM_OUT, the active state is highlighted in the state machine, and the substate information is shown. The LTSSM state output is also logged in the SmartDebug log window. See the following figure.

Config Space Parameter Information

(Ask a Question)When you click on a PCIE instance in the PCIE Hierarchy, the config space parameter data is retrieved from the device and displayed to the right of the LTSSM state machine, as shown in the following example figure. When no PCIE instance is selected, or any level of hierarchy instance except for the PCIE instance is selected, the parameter values are displayed as “NA”. If there is an error retrieving parameter data, the value displayed is “Error” in the GUI.

The list of config parameters and values is also logged in the SmartDebug log window, as shown in the following figure.

Click the Refresh button to update all PCIE data displayed in the GUI.

Record Actions

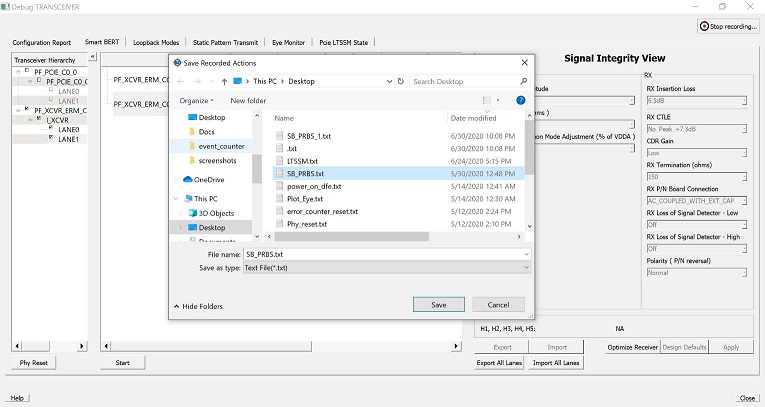

(Ask a Question)This option is used to record the register sequence of XCVR operations into a file. The Start record Actions option is shown at the top-right corner as an option to click to start recording.

This option is hidden in Demo Mode. When you click Start record Actions, recording starts and the option changes to Stop recording….

When you click Stop recording… to stop the recording, a window

prompts you to save the output a text (.txt) file. After saving the

file, the Debug TRANSCEIVER window reverts to default state.

Recorded Content

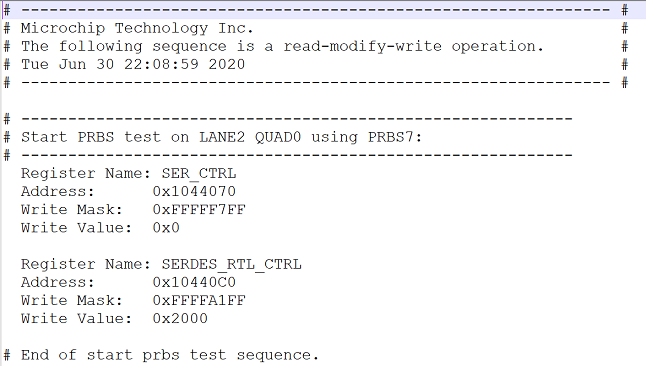

(Ask a Question)The saved file is in plain text (.txt) format.

The first five lines contain the header. The header says that the following sequence is a read-modify-write operation. It also has the date and time of recording.

The operation sequence always starts with the name of the operation followed by the Quad and lane information if applicable.

The following snippet is an example demo file which records PRBS start sequence. Interpreting the text is as follows:

Example 1

- Start PRBS test on LANE2 QUAD0

using PRBS7 means:

- The lane selected on the SmartBERT tab is Q0_ANE0 and the pattern selected is XCVR PMA PRBS7.

- The first set of lines has

the following four subheadings:

Register Name: Register name that can be looked up in the register map.

Address: The physical address of this register is 7 hexadecimal digits. It is calculated based on the Quad, lane number, register type, and offset.

Write Mask: Write mask is an 8 hexadecimal-digit number that indicates the mask value to be applied on the register read value.

Write Value: The write value is 8 hexadecimal digits number to be written after the mask is applied.

If the value is 0, the operation is basically read the register value and apply the mask on it and write in the register.

- End of start PRBS test sequence denotes that the sequence for that lane is completed and the next sequence is initiated.

The following are XCVR operations for which Record Actions is supported:

- SmartBERT tests

- Loopback tests

- Static Pattern tests

- Power ON/OFF Eye Monitor

- Signal Integrity

- Transceiver PHY Reset

- Poll PCIe LTSSM State

- Read PCIe configuration space

The following are XCVR operations for which Record Actions is not supported:

- Eye Monitor

- Optimize Receiver

- PRBS tests from SmartBERT IP

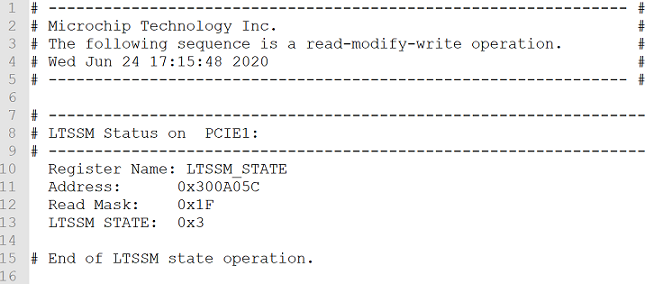

Example 2

LTSSM state on PCIe lane

Register Name and Address will be common to all the register sequence.

Read Mask: This means the sequence is only a read register operation. The mask value is the mask to extract the required field value. Here, the mask value is 0x1F, which means reg[4:0] is the value to be read, hence the mask value.

LTSSM STATE: This is the result that is obtained after the mask is applied to the read value.

15.3.3.2.3 MSS Register Access (PolarFire SoC)

(Ask a Question)The MSS Register Access window comprises the Register Selection and Register Operations panes.

The following table describes the various options available on the MSS Register Access window.

| Option | Description |

|---|---|

| Register Selection | Lists all the instances of the MSS block as described in the MSS register map. Peripherals are shown based on the configuration from the MSS component. Apart from peripherals, the following six instances of registers are always shown in the pane as they are the configuration registers and are always accessible.

|

| Register Filter | Allows you to search for instances/register by their names. Supports wildcard (*) searches.

|

| Register Hierarchy | Displays Instance name and Register name in a two-level hierarchy-level format.

|

| Export All | Exports information of all registers that are displayed in the selection pane to the specified.csv file.

|

| Register Operations | Lists the registers selected for access operations such as read, write, and export. Note: Selected registers are retained even if you

close and re-open the SmartDebug project in the standalone

SmartDebug tool.

|

| Import | Click to load the registers from a .csv file that is

exported. This option loads the register list in the selected pane. Any

registers selected earlier will be prompted to delete or cancel the load

operation.. |

| Delete All | Click to delete all selected registers. |

| Read | Read all selected registers by their register names and display the values in the hexadecimal format. |

| Write | Each cell in the table of selected registers can be accessed

individually to write the values in hexadecimal format.

|

| Export | Reads the values of selected registers and saves them in the

specified .csv file. The exported

.csv file contains six sections

|

15.3.3.2.4 Debug IOD

(Ask a Question)PF_IOD_GENERIC_RX IP instance is configured as Dynamic or

Fractional Dynamic mode in the design. Click the Debug IOD button

on the main SmartDebug window to access this feature. The IOD Tap Delays window lists the

PF_IOD_GENERIC_RX IP instances available in the design in the

Choose IOD drop-down list. Select an IOD instance and click

the Get Training Data button to view the Bit Align IP instances

and corresponding Delay Tap values.

The following figure shows a design example with two instances of

CORERXIODBITALIGN IP and the tap delay values read from those

instances.

CORERXIODBITALIGN IP must have

the output debug pins either connected or promoted to the top for SmartDebug to detect

and identify the debug signals.The following figure shows the SmartDebug Log window when the training is successful.

The following figure shows the IOD Tap Delays window when the training fails.

The following figure shows the SmartDebug Log window when the training fails.

15.3.3.2.5 Debug UPROM

(Ask a Question)You can debug clients configured in a design and debug µPROM memory address information with the Debug UPROM feature.

In the main SmartDebug window, click Debug UPROM.

If a µPROM memory block is used in the Libero design, the UPROM Debug window appears.

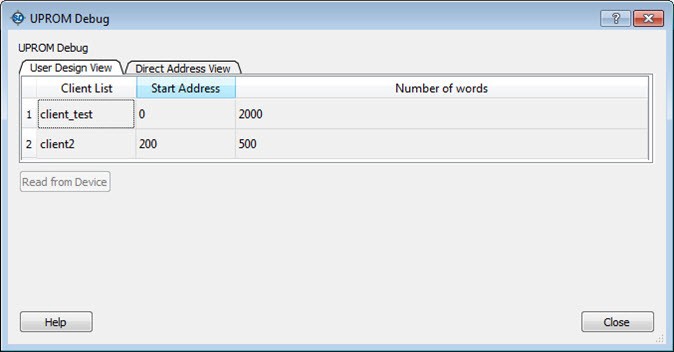

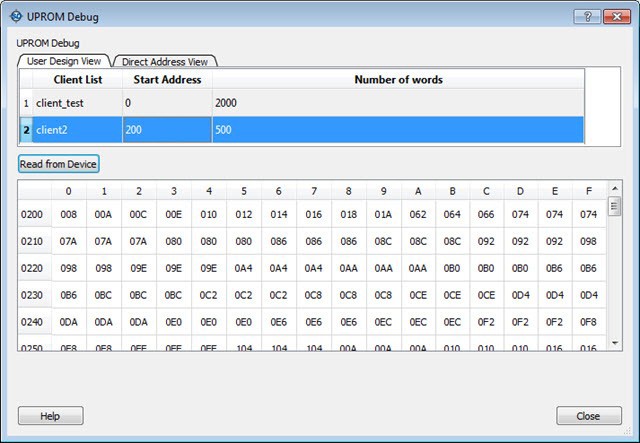

User Design View

(Ask a Question)The User Design View tab in the µPROM Debug window lists all clients configured in the design. Selecting a client in the list enables the Read from Device button.

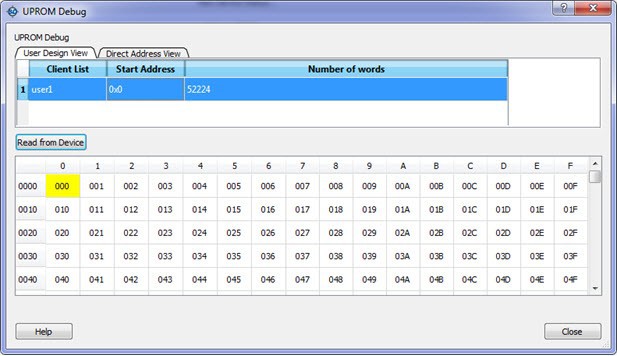

Click the Read from Device button to display a table showing the data in the location at the selected client address. See the following figure.

The Client address is associated with Start Address and Number of 9-bit words. Therefore, the table will contain as many locations as the number of 9-bit words.

In the preceding example, Number of 9-bit words is 52224, so 52224 words will be shown in the table. Column headers are numbered 0 to F in hexadecimal format, representing 16 words in a row.

Row addresses begin with a word address associated with Start Address. For example, if the Start Address is 0x15 (hex), the starting row has an address of 0x0010.

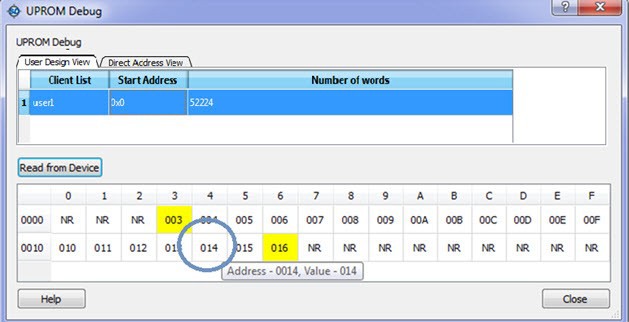

Hover your cursor over a cell to see the cell’s address and value, as shown in the following figure.

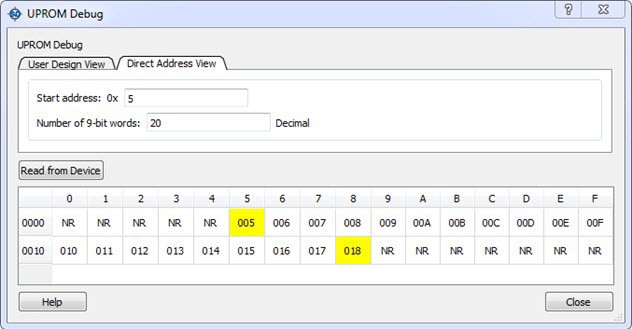

Direct Address View

(Ask a Question)The Direct Address View tab in the µPROM Debug window provides access to µPROM memory. You can read a part of a client or more than one client by specifying the Start Address and Number of 9-bit words.

Start Address: Hexadecimal value (0 -9, A-F, upper/lower case)

Values are validated and errors are indicated by a red "STOP" icon. The error message displays when you hover your cursor over the icon.

Number of 9-bit words: Positive integer value

Values are validated and errors are indicated by a red "STOP". The error message displays when you hover your cursor over the icon.

Read from Device: Disabled until valid values are entered in the fields.

Invalid or blank values are indicated by a red "STOP". The error message displays when you hover your cursor over the icon.

- When one field is entered, both fields are validated and the Read from Device button is enabled.

- If fields change after enabling Read from Device, values are validated again and Read from Device may be disabled if invalid values are entered.

- If the µPROM Debug window is closed and reopened, the session is retained. The µPROM Debug session is lost only if the main SmartDebug window is closed.

Demo Mode